Intel

®

IXP43X Product Line of Network Processors

April 2007 HDG

Document Number: 316844; Revision: 001US 47

Hardware Design Guidelines—Intel

®

IXP43X Product Line of Network Processors

3.11.2 PCI Interface Block Diagram

While using the IXP43X network processors in Master mode, the PCI module can

interface to up to four PCI cards (devices) at 33 MHz. The limitation is due to load

requirements to maintain signal integrity.

The PCI-to-PCI bridge must be used to address the PCI requirement not to exceed one

load per PCI connector unless it is through a PCI-to-PCI bridge.

The IDSEL signals on the PCI slots can be connected to one of the PCI_AD lines,

preferable to the higher order address signals. Reset support can be accomplished by

using one of the GPIO pins to generate a reset or through an external decoder of the

Expansion bus.

PCI_INTA_N O/D Yes

Interrupt A.

When this interface/signal is enabled and is used or not used in a system design, the

interface/signal should be pulled high with a 10-KΩ resistor.

PCI_CLKIN I Yes

Clock input.

When this interface/signal is enabled and is not being used in a system design, the interface/

signal should be pulled high with a 10-KΩ resistor.

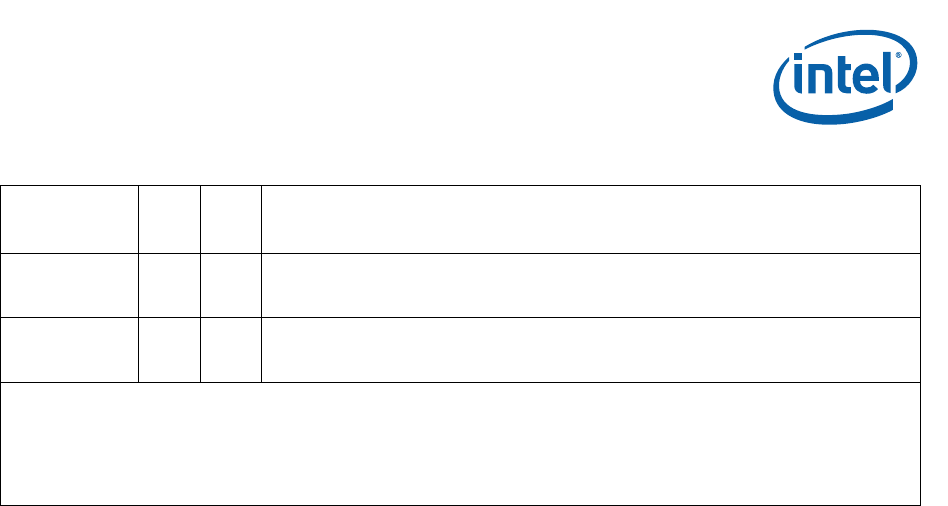

Table 17. PCI Controller (Sheet 2 of 2)

Name

Type

Field

Pull

Up/

Down

Recommendations

Notes:

1. Features disabled/enabled by Soft Fuse must be done during the boot-up sequence. A feature cannot be enabled after

being disabled without asserting a system reset.

2. Features disabled by a specific part number, do not require pull-ups or pull-downs. Therefore, all pins can be left

unconnected.

3. Features enabled by a specific part number — and required to be Soft Fuse-disabled, as stated in Note 1 — only require

pull-ups or pull-downs in the clock-input signals.