Intel

®

IXP43X Product Line of Network Processors

April 2007 HDG

Document Number: 316844; Revision: 001US 43

Hardware Design Guidelines—Intel

®

IXP43X Product Line of Network Processors

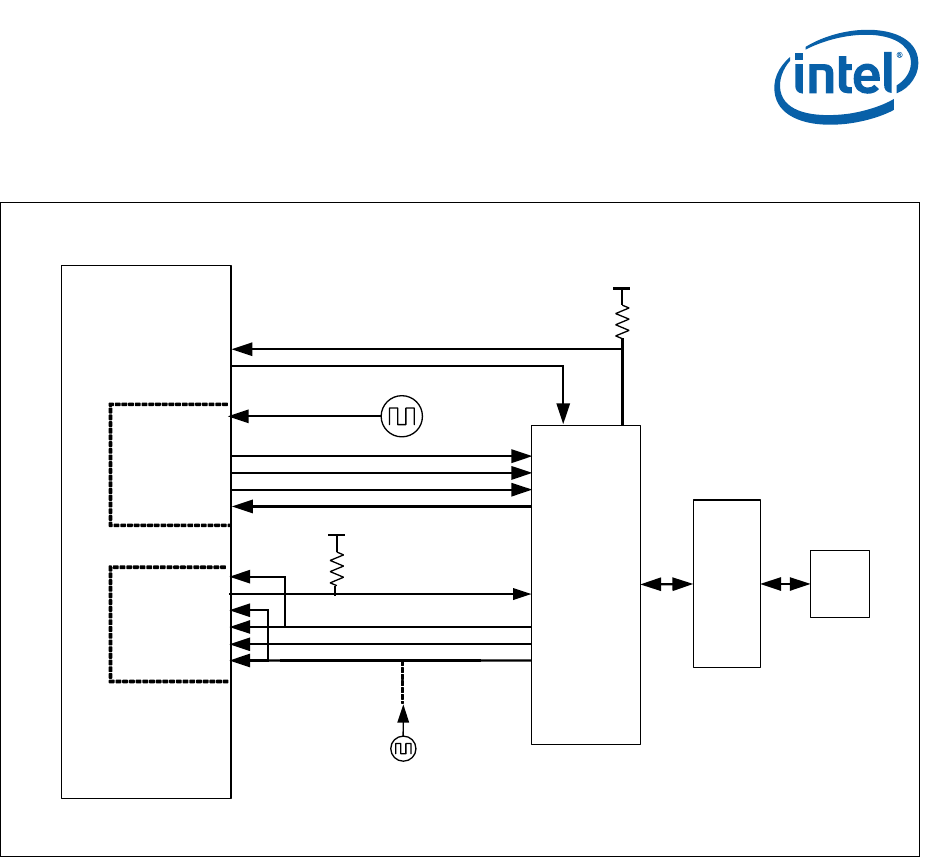

3.10 SSP Interface

The IXP43X network processors have a Synchronous Serial Peripheral Interface (SSP)

module. Its primary function is to provide connectivity between the Intel XScale

®

Processor and an external SSP interface.

The SSP module supports Texas Instruments synchronous serial protocol (SSP)*,

Motorola serial peripheral interface (SPI)* and National Microwire*.

The clock rate can be selected from an internal, 3.6864-MHz source or external source

fed at input pin SSP_EXTCLK. The clock can then be divided down anywhere from

7.2 KHz to 1.84 MHz by setting bits 15:08 in SSP Control Register 0 (SSCR0). For

instructions on the SSP configuration register, refer to the Serial Clock Register (SCR)

subsection in the Memory Controller chapter of the Intel

®

IXP43X Product Line of

Network Processors Datasheet.

Figure 11. HSS Interface Example

HSS_TX_FRAME0

HSS_TXDATA0

HSS_TXCLK0

HSS_RXFRAME0

HSS_RXDATA0

HSS_RXCLK0

HSS Interface

RJ11

DTX

PCLK

FSYNC

SLIC CODEC

RXD

AFE

RESET_N

Vccp (3.3 V)

10 KΩ

512 KHz to

8.192 MHz

Clock derived from

SLIC/CODEC

or external oscilator

SSP_TXD

SSP_SFRM

SSP_EXTCLK

SSP_SCLK

SSP_RXD

D I

CS_N

CLK

DO

33 MHz

External Oscillator

SSP Interface

GPIO_0

INT_N

Vccp (3.3 V)

10 KΩ

GPIO_1

Clock derived internally

from 3.6864 MHz

or external oscilator

B4108-005

Intel® IXP 43X

Product Line of

Network Processors