Intel

®

IXP43X Product Line of Network Processors

April 2007 HDG

Document Number: 316844; Revision: 001US 85

Hardware Design Guidelines—Intel

®

IXP43X Product Line of Network Processors

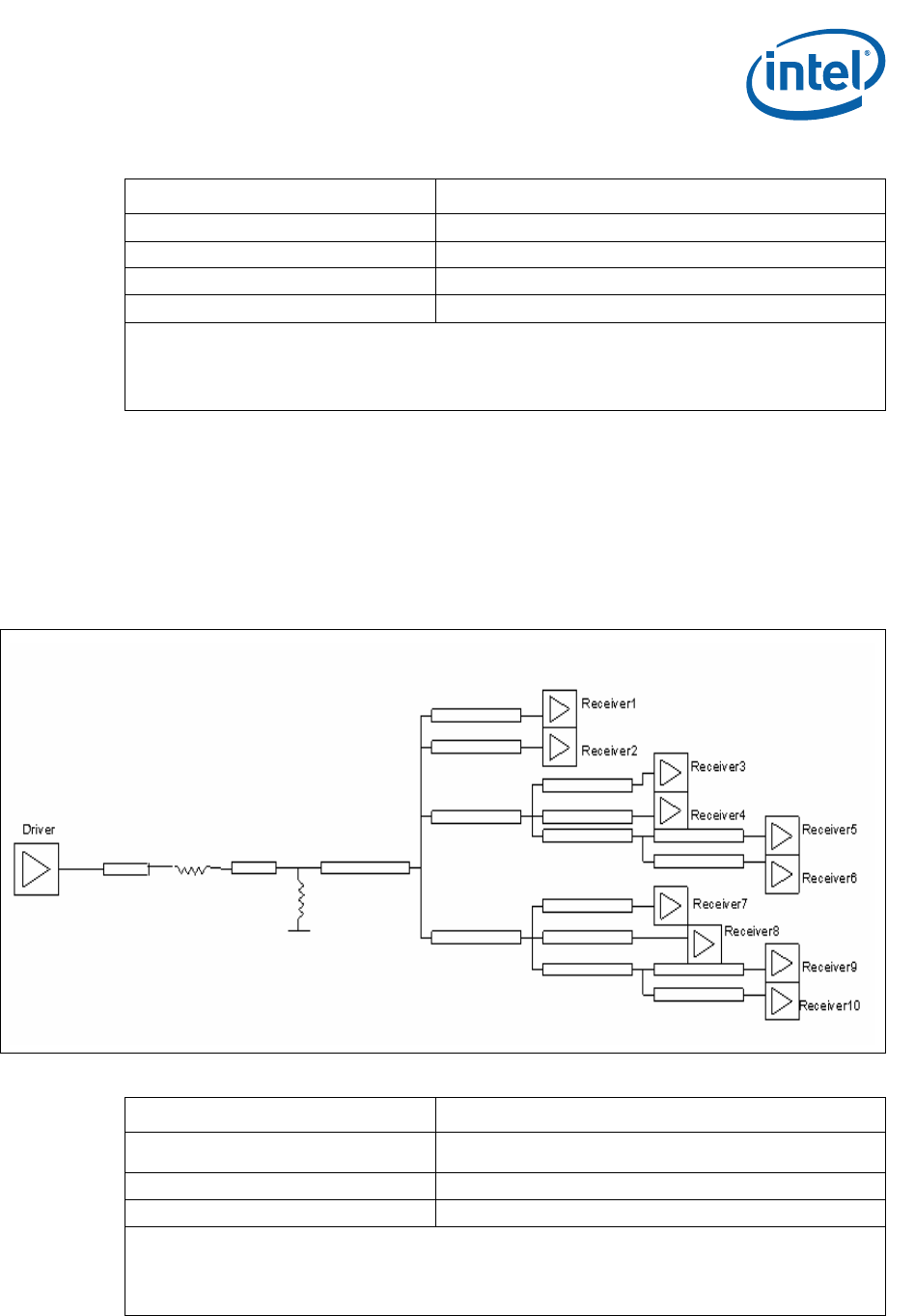

7.3.3.3 Command Groups

The command signal groups include all signals D_MA[13:0]/DDR_MA[13:0],

D_BA[1:0]/DDR_BA[1:0], D_RAS/DDR_RAS, D_CAS/DDR_CAS and D_WE/DDR_WE.

The groups should be routed on internal layers, except for pin escapes. It is

recommended that pin escape vias be located directly adjacent to the ball pads on all

signals. Surface layer routing should be minimized. The following table provides routing

guidelines for signals within these groups.

Minimum Spacing to Other DDR Signals 20.0 mils

Minimum Spacing to non-DDR Signals 25.0 mils

Maximum Via Count 5 per trace

Total Trace Length 1000 mils to 2000 mils

Table 35. DDRII Data and Control Signal Group Routing Guidelines

Parameter Definition

Notes:

1. Nominal trace width is determined by board physical characteristics and stack-up. This value should

be verified with the PWB manufacturer to achieve the desired Zo.

2. Nominal pair to pair spacing is determined by board physical characteristics and stack-up. This value

should be verified with the PWB manufacturer to achieve the desired Zdiff.

Figure 34. DDRII Command Simulation Results: ADDRESS signals

Table 36. DDRII Command Signal Group Routing Guidelines

Parameter Definition

Signal Group Members

D_MA[13:0]/DDR_MA[13:0], D_BA[1:0]/DDR_BA[1:0], D_RAS/DDR_RAS,

D_CAS/DDR_CAS and D_WE/DDR_WE.

Topology Point to Point (1 Driver, 10Receivers)

Single Ended Trace Impedance (Z

o

) 50 Ω

Notes:

1. Nominal trace width is determined by board physical characteristics and stack-up. This value should

be verified with the PWB manufacturer to achieve the desired Zo.

2. Nominal pair to pair spacing is determined by board physical characteristics and stack-up. This value

should be verified with the PWB manufacturer to achieve the desired Zdiff.

20ohm20ohm