Intel

®

IXP43X Product Line of Network Processors—Hardware Design Guidelines

Intel

®

IXP43X Product Line of Network Processors

HDG April 2007

72 Document Number: 316844; Revision: 001US

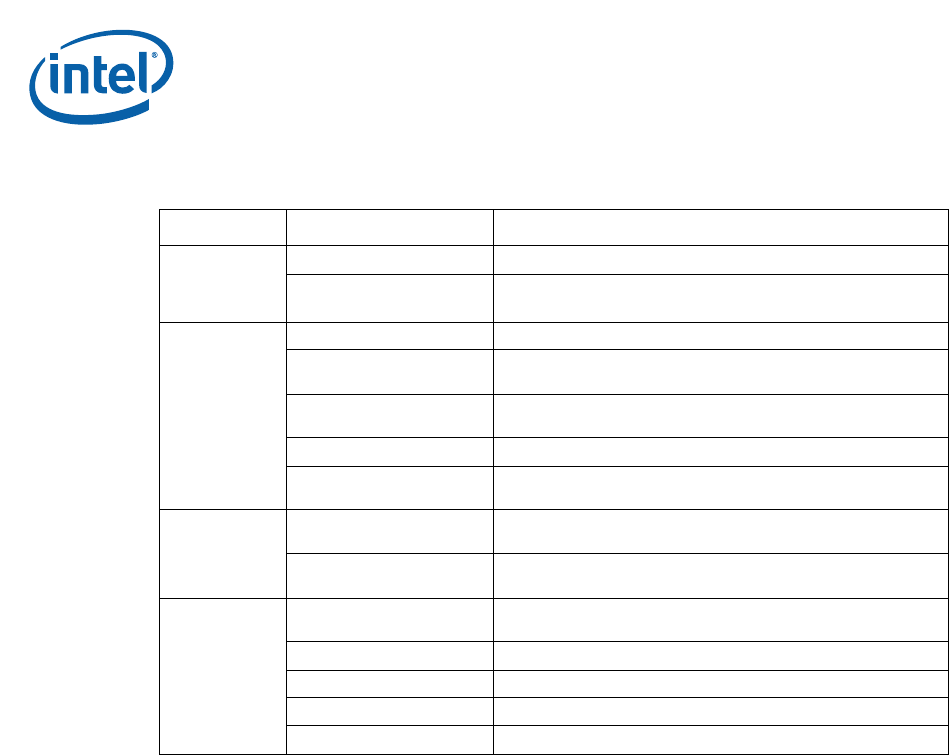

Table 24. DDRII/I Signal Groups

Group Signal Name Description

Clocks

D_CK[2:0] / DDR_CK[2:0] DDRII/I SDRAM Differential Clocks

D_CK_N[2:0] /

DDR_CK_N[2:0]

DDRII/I SDRAM Inverted Differential Clocks

Data

D_CB[7:0] / DDR_CB[7:0] ECC Data

D_DQ[31:0] /

DDR_DQ[31:0]

Data Bus

D_DQS[4:0] /

DDR_DQS[4:0]

Data Strobes

D_DQS_N[4:0] Complementary Data Strobes

D_DM[4:0] /

DDR_DM[4:0]

Data Mask

Control

D_CKE[1:0] /

DDR_CKE[1:0]

Clock Enable - one per bank

D_CS_N[1:0] /

DDR_CS_N[1:0]

Chip Select - one per bank

Command

D_MA[13:0] /

DDR_MA[13:0]

Address Bus

D_BA[1:0] / DDR_BA[1:0] Bank Select

D_RAS_N / DDR_RAS_N Row Address Select

D_CAS_N / DDR_CAS_N Column Address Select

D_WE_N / DDR_WE_N Write Enable