Intel

®

IXP43X Product Line of Network Processors

April 2007 HDG

Document Number: 316844; Revision: 001US 41

Hardware Design Guidelines—Intel

®

IXP43X Product Line of Network Processors

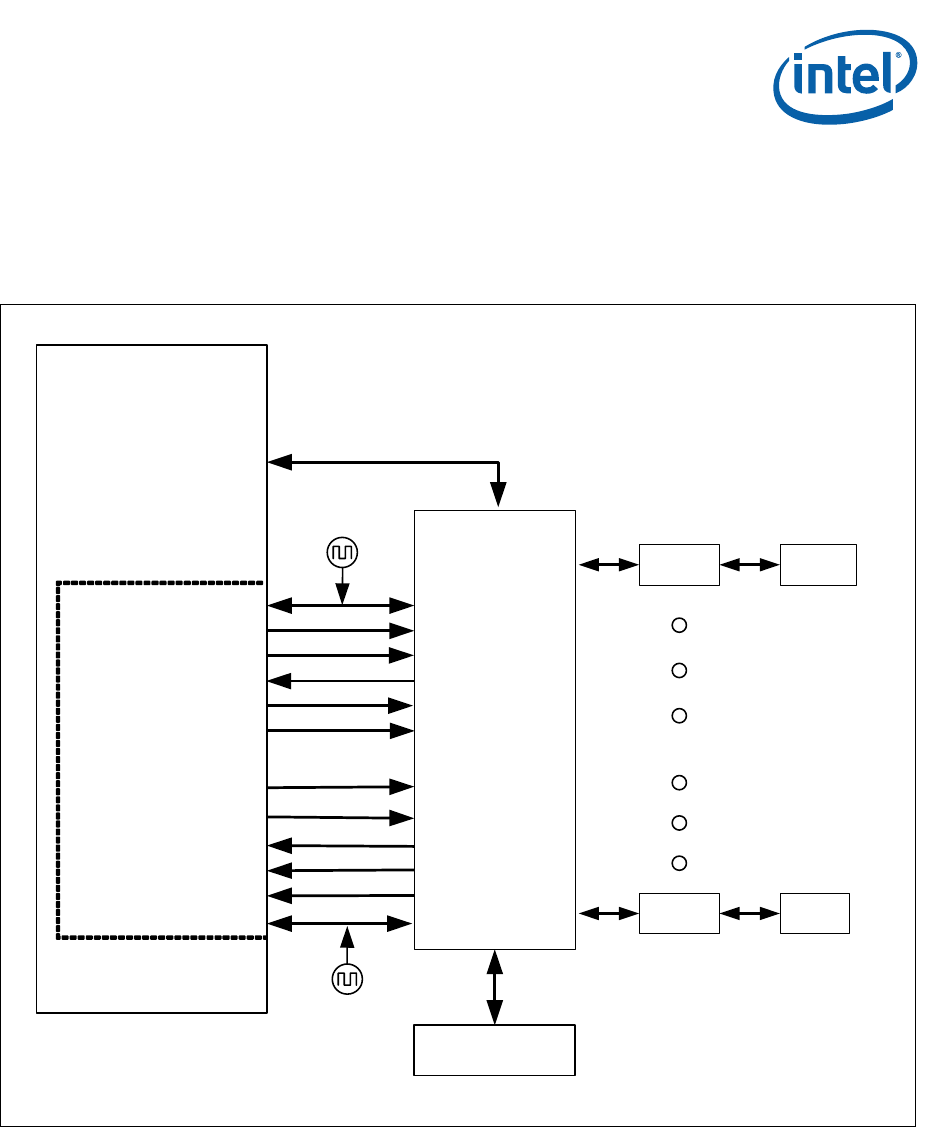

3.8.2 Device Connection

The following example shown in Figure 10 shows a typical interface to an ADSL Framer

via the UTOPIA bus. Notice that depending on the framer used some control signals

might be required which can be derived from the Expansion bus or the GPIO signals.

3.9 HSS Interface

NPE A has an integrated High-Speed Serial (HSS) module, whose primary function is to

provide connectivity between the internal NPE A and the external HSS interface. There

is one HSS port that can directly interface to SLIC/CODEC devices for voice

applications, or serial DSL framers. The HSS ports are software configurable to support

various serial protocols, such as T1/ E1/J1, and MVIP. For a list of supported protocols,

see the Intel

®

IXP400 Software Programmer’s Guide.

Figure 10. UTOPIA Interface Example

UTP_OP_CLK

UTP_OP_DATA[7:0]

UTP_OP_ADDR[4:0]

UTP_OP_SOC

UTP_OP_FCO

UTP_OP_FCI

UTP_IP_CLK

UTP_IP_DATA[7:0]

UTP_IP_ADDR[4:0]

UTP_IP_SOC

UTP_IP_FCO

Intel® IXP43X

Product Line of

Network

Processors

UTOPIA Level 2

Interface

TXCLK

TXDATA[7:0]

TXADDR[4:0]

TXSOC

TXENB#

TXCLAV

RXCLK

RXDATA[7:0]

RXADDR[4:0]

RXSOC

RXENB#

UTP_IP_FCI RXCLAV

ATM Layer Device

ADSL Framer

Multi-Channel

AFE RJ11

Analog Front

End

AFE RJ11

SDRAM

Local Memory

EX_BUS

25 MHz

25 MHz

Control Signals

B4107-005