Intel

®

IXP43X Product Line of Network Processors

April 2007 HDG

Document Number: 316844; Revision: 001US 31

Hardware Design Guidelines—Intel

®

IXP43X Product Line of Network Processors

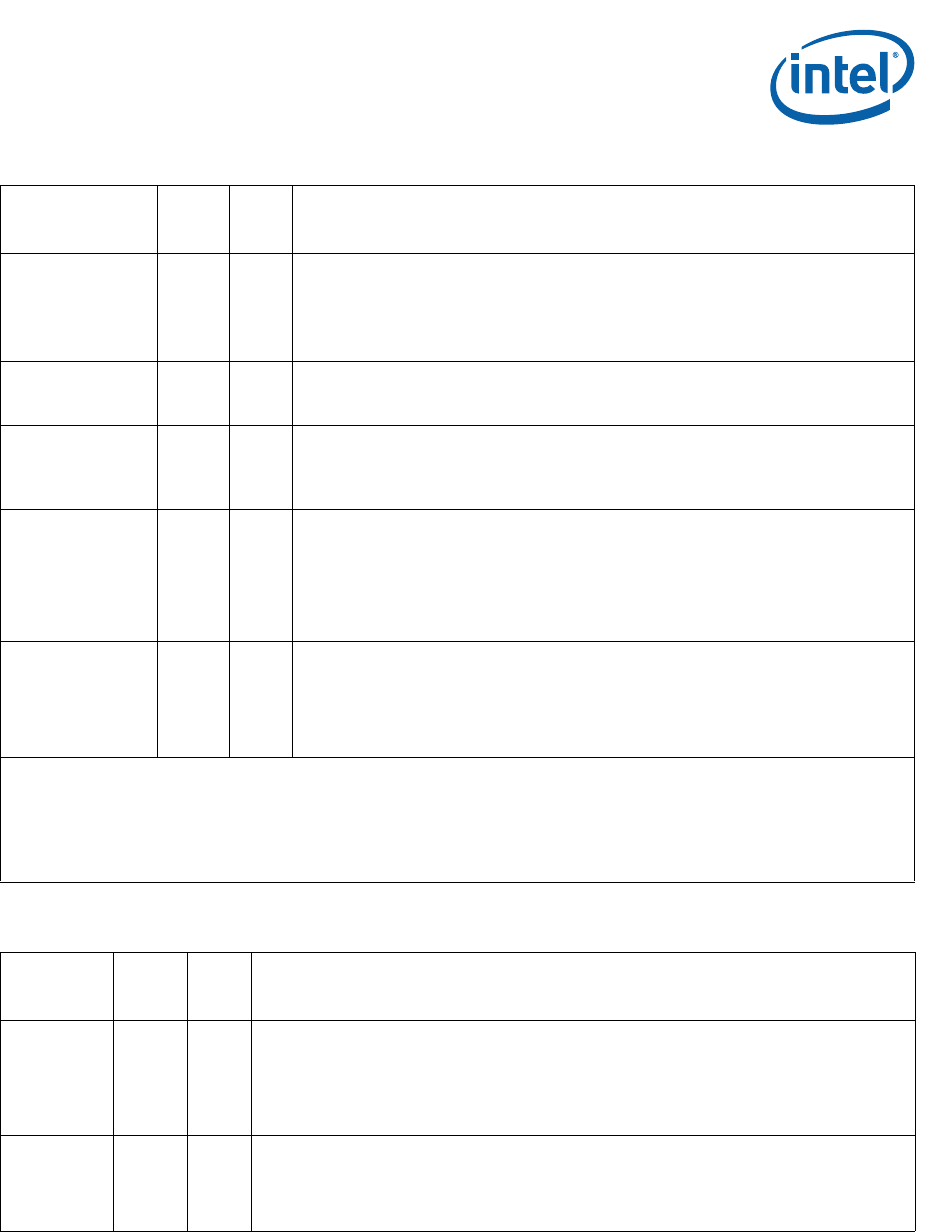

3.5.2 Device Connection, MII

Figure 6 is a typical example of an Ethernet PHY device interfacing to one of the MACs

via the MII hardware protocol.

ETHC_rxclk I Yes

Externally supplied receive clock:

• 25 MHz for 100 Mbps operation

•2.5MHz for 10Mbps

This MAC contains hardware hashing capabilities that are local to the interface.

Should be pulled high through a 10-KΩ resistor when not being utilized in the system.

ETHC_rxdATA[3:0] I Yes

Receive data bus from PHY, data sampled synchronously, with respect to ETHC_RXCLK.

This MAC contains hardware hashing capabilities that are local to the interface.

Should be pulled high through a 10-KΩ resistor when not being utilized in the system.

ETHC_rxdv I Yes

Receive data valid is used to inform the MII interface about data that is being sent by

the Ethernet PHY

This MAC contains hardware hashing capabilities that are local to the interface.

Should be pulled high through a 10-KΩ resistor when not being utilized in the system.

ETHC_col I Yes

Asserted by the PHY when a collision is detected by the PHY. This MAC contains

hardware hashing capabilities that are local to the interface.

Should be pulled high through a 10-KΩ resistor when not being utilized in the system

When this interface is disabled through the NPE-C Ethernet soft fuse (refer to the

Expansion Bus Controller chapter of the Intel

®

IXP43X Product Line of Network

Processors Developer’s Manual) and is not being used a system design, this interface/

signal is not required for any connection.

ETHC_crs I Yes

Asserted by the PHY when the transmit medium or receive medium are active.

De-asserted when both the transmit and receive medium are idle. Remains asserted

throughout the duration of collision condition. PHY asserts CRS asynchronously and

de-asserts synchronously with respect to ETHC_RXCLK.

This MAC contains hardware hashing capabilities that are local to the interface.

Should be pulled high through a 10-KΩ resistor when not being utilized in the system.

Notes:

1. Features disabled/enabled by Soft Fuse must be done during the boot-up sequence. A feature cannot be enabled after

being disabled without asserting a system reset.

2. Features disabled by a specific part number, do not require pull-ups or pull-downs. Therefore, all pins can be left

unconnected.

3. Features enabled by a specific part number — and required to be Soft Fuse-disabled, as stated in note 1 — only require

pull-ups or pull-downs in the clock-input signals.

Table 11. MAC Management Signal Recommendations - NPE A and NPE C

Name

Type

Field

Pull

Up/

Down

Recommendations

ETH_mdio IO Yes

NPE A and NPE C

Management data input output. Provides the write data to both PHY devices connected to

each MII interface. An external pull-up resistor of 1.5K ohm is required on

ETHC_MDIO to properly quantify the external PHYs used in the system. For specific

implementation, see the IEEE 802.3 specification.

Should be pulled high through a 10-KΩ resistor when not being utilized in the system

ETH_mdc O No

NPE A and NPE C

Management data clock. Management data interface clock is used to clock the MDIO signal as

an output and sample the MDIO as an input. The ETHC_MDC is an input on power up and can

be configured to be an output through Intel APIs documented in the Intel

®

IXP400 Software

Programmer’s Guide

Table 10. MII NPE C Signal Recommendations (Sheet 2 of 2)

Name

Type

Field

Pull

Up/

Down

Recommendations