S/UNI-QUAD

PMC-Sierra, Inc.

PM5349 S/UNI-QUAD

DATASHEET

PMC-971239 ISSUE 6 SATURN USER NETWORK INTERFACE (155-QUAD)

Proprietary and Confidential to PMC-Sierra, Inc., and for its Customers’ Internal Use

105

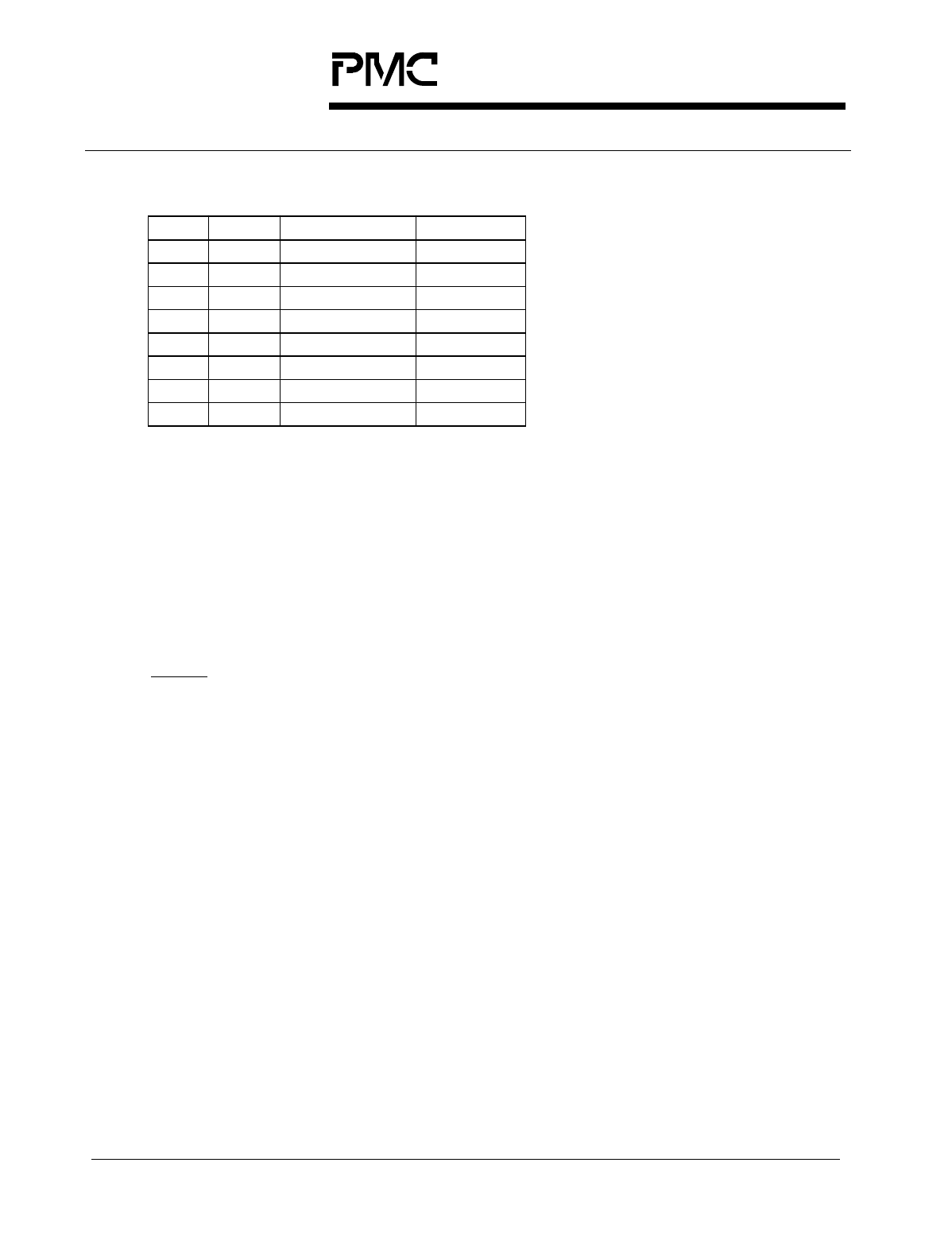

Register 0x31 (EXTD=1): RPOP Interrupt Status

Bit Type Function Default

Bit 7 Unused X

Bit 6 Unused X

Bit 5 Unused X

Bit 4 Unused X

Bit 3 Unused X

Bit 2 Unused X

Bit 1 Unused X

Bit 0 R ERDII X

NOTE: To facilitate additional register mapping, shadow registers have been

added to registers 0x30, 0x31 and 0x33. These shadow registers are accessed in

the same way as the normal registers.

The EXTD (extend register) bit must be set in register 0x36 to allow switching

between accessing the normal registers and the shadow registers

This register allows identification and acknowledgment of path level alarm and

error event interrupts.

ERDII:

The ERDII bit is set to logic one when a change is detected in the received

enhanced RDI state. ERDII is cleared when the RPOP Interrupt Status

register is read.