S/UNI-QUAD

PMC-Sierra, Inc.

PM5349 S/UNI-QUAD

DATASHEET

PMC-971239 ISSUE 6 SATURN USER NETWORK INTERFACE (155-QUAD)

Proprietary and Confidential to PMC-Sierra, Inc., and for its Customers’ Internal Use

22

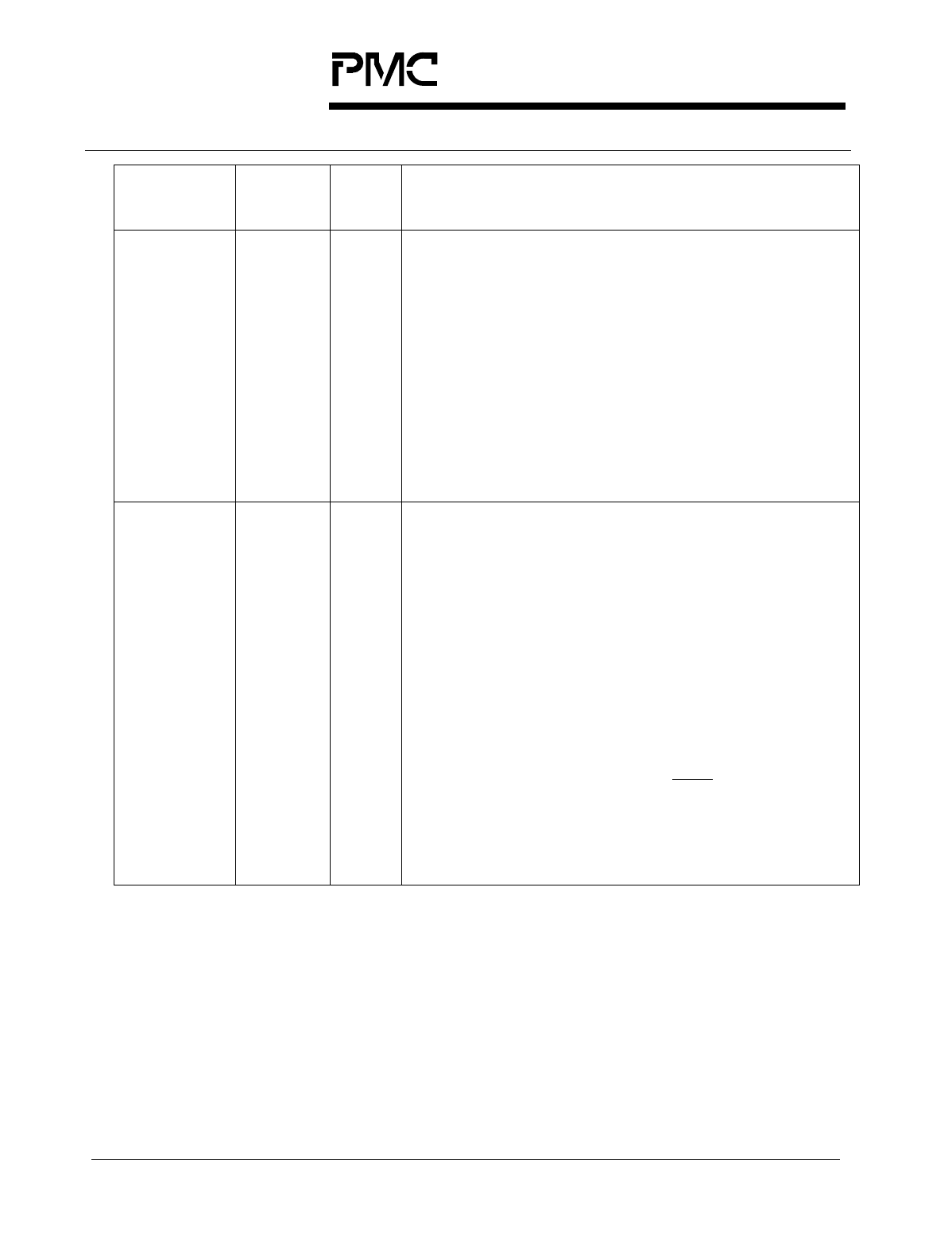

Pin Name Type Pin

No.

Function

DRCA[4]

DRCA[3]

DRCA[2]

DRCA[1]

Output M21

N23

N22

N21

UTOPIA Direct Receive Cell Available (DRCA[4:1]).

These output signals provides direct status

indication of when a cell is available in the receive

FIFO for the corresponding port. DRCA can be

configured to be de-asserted when either zero or

four bytes remain in the selected/addressed FIFO.

DRCA will thus transition low on the rising edge of

RFCLK after Payload word 24 (RCALEVEL0=1) or

19 (RCALEVEL0=0) is output if the PHY being

polled is the same as the PHY in use.

DRCA[x] is updated on the rising edge of RFCLK.

PHY_OEN Input A19 The PHY Output Enable (PHY_OEN) signal controls

the operation of the system interface. When set to

logic zero, all System Interface outputs are held

tristate. When PHY_OEN is set to logic one, the

interface is enabled. PHY_OEN can be overwritten

by the PHY_EN Master System Interface

Configuration register bit. PHY_OEN and PHY_EN

are OR’ed together to enable the interface.

When the S/UNI-QUAD is the only PHY layer device

on the bus, PHY_OEN can safely be tied to logic

one. When the S/UNI-QUAD shares the bus with

other devices, then PHY_OEN must be tied to logic

zero, and the PHY_EN register bit used to enable

the bus once its PHY_ADR[2:0] is programmed in

order to avoid conflicts.