S/UNI-QUAD

PMC-Sierra, Inc.

PM5349 S/UNI-QUAD

DATASHEET

PMC-971239 ISSUE 6 SATURN USER NETWORK INTERFACE (155-QUAD)

Proprietary and Confidential to PMC-Sierra, Inc., and for its Customers’ Internal Use

133

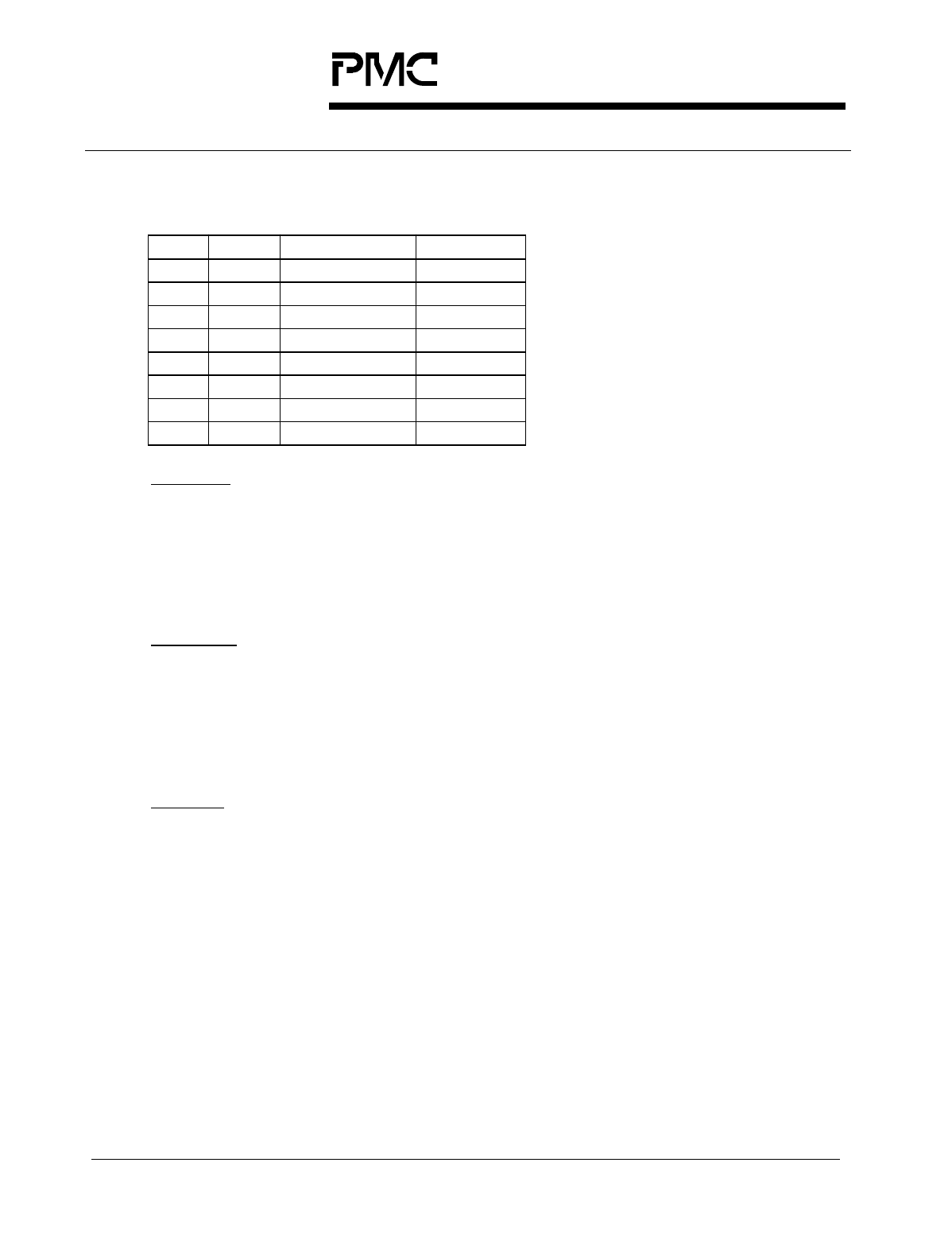

Register 0x60: RXCP Configuration 1

Bit Type Function Default

Bit 7 R/W DDSCR 0

Bit 6 R/W Reserved 0

Bit 5 Unused X

Bit 4 Unused X

Bit 3 Unused X

Bit 2 R/W HCSADD 1

Bit 1 R/W Reserved 0

Bit 0 R/W DISCOR 0

DISCOR:

The DISCOR bit controls the HCS error correction algorithm. When DISCOR

is a logic zero, the error correction algorithm is enabled, and single-bit errors

detected in the cell header are corrected. When DISCOR is a logic one, the

error correction algorithm is disabled, and any error detected in the cell

header is treated as an uncorrectable HCS error.

HCSADD:

The HCSADD bit controls the addition of the coset polynomial, x

6

+x

4

+x

2

+1, to

the HCS octet prior to comparison. When HCSADD is a logic one, the

polynomial is added, and the resulting HCS is compared. When HCSADD is

a logic zero, the polynomial is not added, and the unmodified HCS is

compared.

DDSCR:

The DDSCR bit controls the de-scrambling of the cell payload with the

polynomial x

43

+ 1. When DDSCR is set to logic one, cell payload de-

scrambling is disabled. When DDSCR is set to logic zero, payload de-

scrambling is enabled.