S/UNI-QUAD

PMC-Sierra, Inc.

PM5349 S/UNI-QUAD

DATASHEET

PMC-971239 ISSUE 6 SATURN USER NETWORK INTERFACE (155-QUAD)

Proprietary and Confidential to PMC-Sierra, Inc., and for its Customers’ Internal Use

60

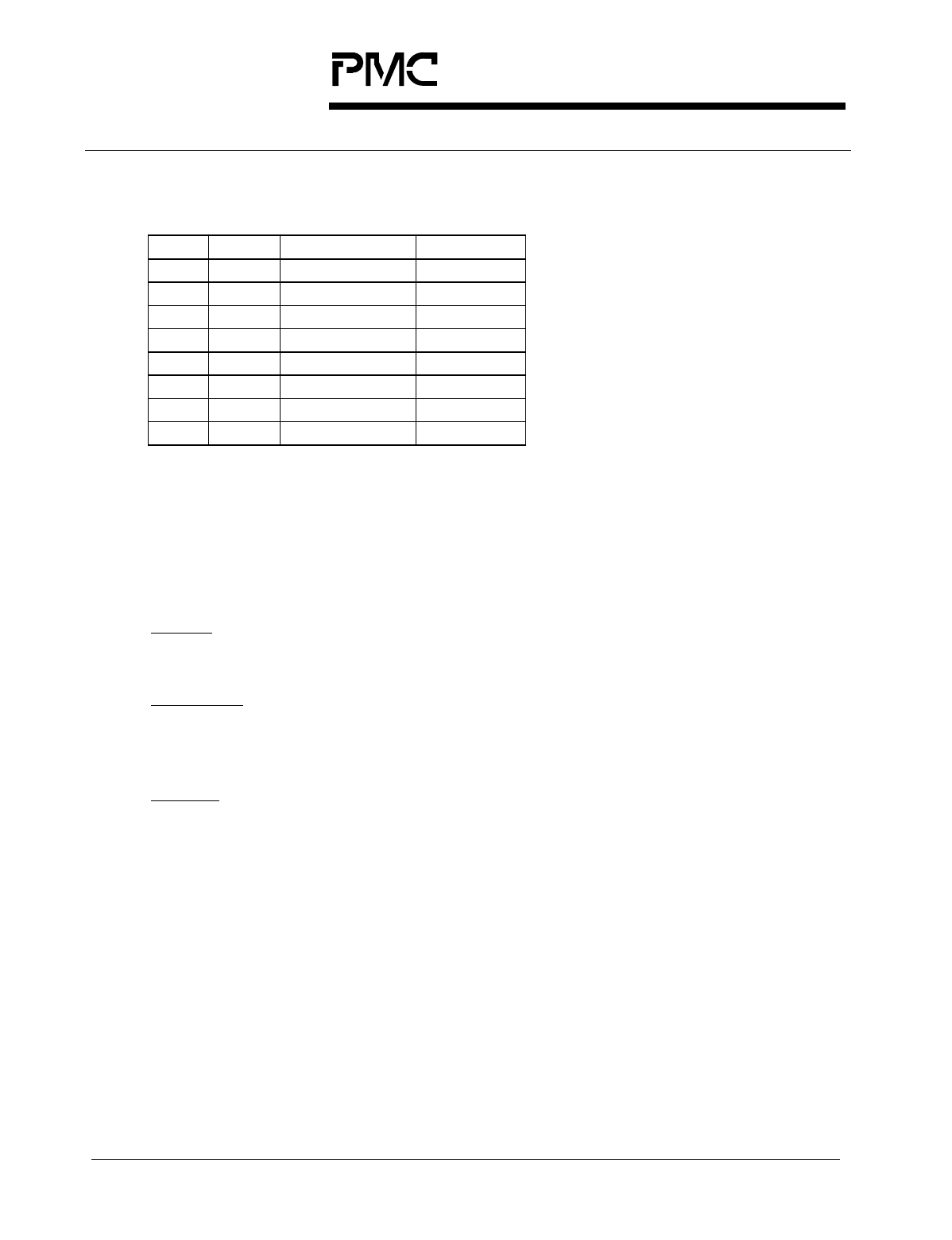

Register 0x00: S/UNI-QUAD Master Reset and Identity

Bit Type Function Default

Bit 7 R/W RESET 0

Bit 6 R TYPE[3] 1

Bit 5 R TYPE[2] 1

Bit 4 R TYPE[1] 1

Bit 3 R TYPE[0] 0

Bit 2 R ID[2] 0

Bit 1 R ID[1] 0

Bit 0 R ID[0] 1

This register allows the revision of the S/UNI-QUAD to be read by software

permitting graceful migration to support newer feature enhanced versions of the

S/UNI-QUAD. It also provides software reset capability.

In addition, writing to this register simultaneously loads all the performance meter

registers in the RSOP, RLOP, RPOP, RXCP and TXCP blocks.

ID[2:0]:

The ID bits can be read to provide a binary S/UNI-QUAD revision number.

TYPE[3:0]:

The TYPE bits distinguish the S/UNI-QUAD from the other members of the

S/UNI family of devices.

RESET:

The RESET bit allows the S/UNI-QUAD to be reset under software control. If

the RESET bit is a logic one, the entire S/UNI-QUAD is held in reset. This bit

is not self-clearing. Therefore, a logic zero must be written to bring the

S/UNI-QUAD out of reset. Holding the S/UNI-QUAD in a reset state places it

into a low power, stand-by mode. A hardware reset clears the RESET bit,

thus negating the software reset. Otherwise, the effect of a software reset is

equivalent to that of a hardware reset.