S/UNI-QUAD

PMC-Sierra, Inc.

PM5349 S/UNI-QUAD

DATASHEET

PMC-971239 ISSUE 6 SATURN USER NETWORK INTERFACE (155-QUAD)

Proprietary and Confidential to PMC-Sierra, Inc., and for its Customers’ Internal Use

155

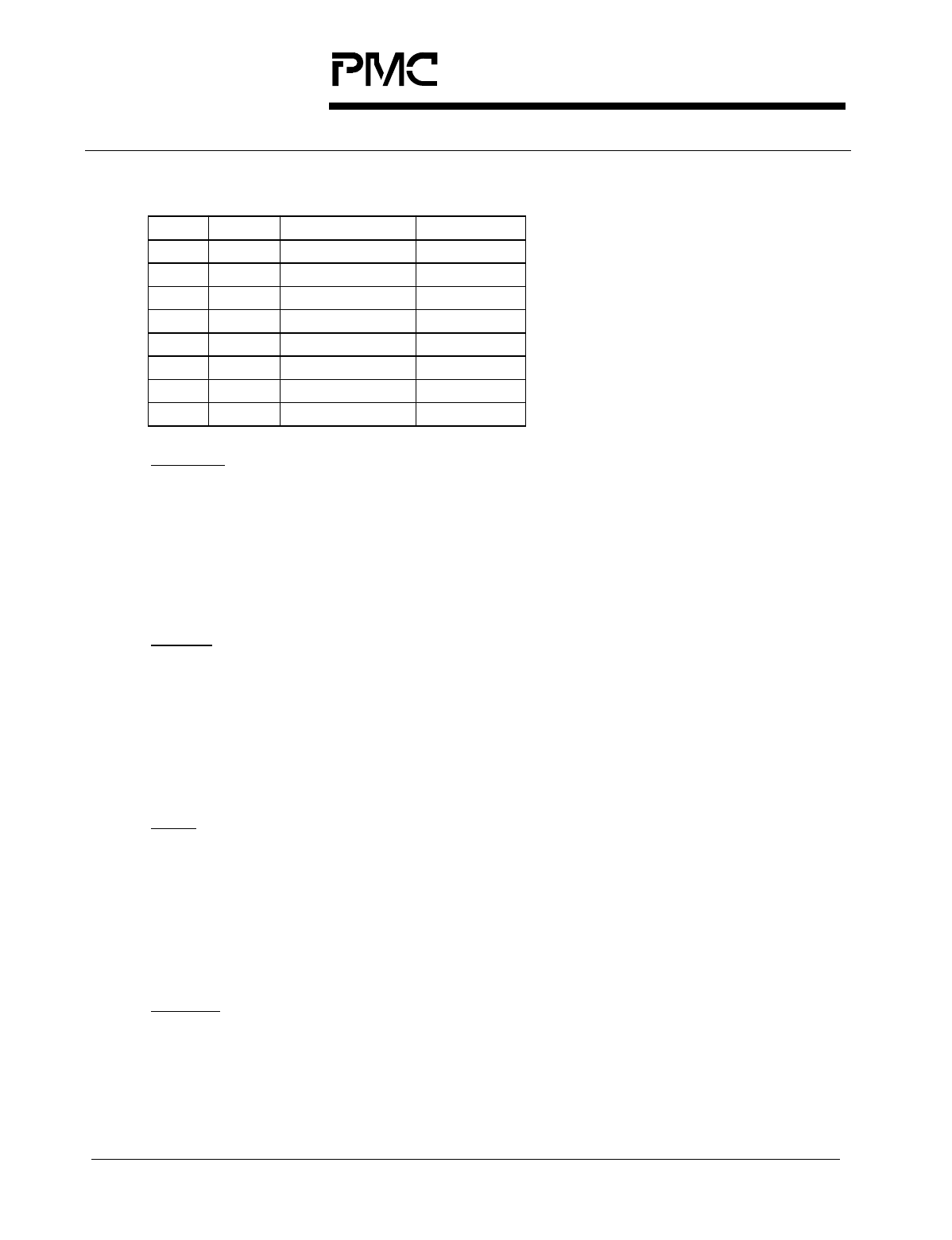

Register 0x82: TXCP Cell Count Status/Configuration Options

Bit Type Function Default

Bit 7 R/W XFERE 0

Bit 6 R XFERI X

Bit 5 R OVR X

Bit 4 Unused X

Bit 3 R/W Reserved 1

Bit 2 R/W H4INSB 0

Bit 1 R/W Reserved 0

Bit 0 R/W Reserved 0

H4INSB:

The active low H4 insert enable, H4INSB, determines the contents of the H4

byte in the outgoing path overhead. If H4INSB is set to logic one, the H4 byte

is set to the value of 00 hexadecimal. If H4INSB is set to logic zero, the H4

byte is set to the cell indicator offset value.

XFERI:

The XFERI bit indicates that a transfer of Transmit Cell Count data has

occurred. A logic one in this bit position indicates that the Transmit Cell Count

registers have been updated. This update is initiated by writing to one of the

Transmit Cell Count register locations or to the S/UNI-QUAD Identification,

Master Reset, and Global Monitor Update register. XFERI is set to logic zero

when this register is read.

OVR:

The OVR bit is the overrun status of the Transmit Cell Count registers. A logic

one in this bit position indicates that a previous transfer (indicated by XFERI

being logic one) has not been acknowledged before the next accumulation

interval has occurred and that the contents of the Transmit Cell Count

registers have been overwritten. OVR is set to logic zero when this register is

read.

XFERE:

The XFERE bit enables the generation of an interrupt when an accumulation

interval is completed and new values are stored in the Transmit Cell Count

registers. When XFERE is set to logic one, the interrupt is enabled.