S/UNI-QUAD

PMC-Sierra, Inc.

PM5349 S/UNI-QUAD

DATASHEET

PMC-971239 ISSUE 6 SATURN USER NETWORK INTERFACE (155-QUAD)

Proprietary and Confidential to PMC-Sierra, Inc., and for its Customers’ Internal Use

92

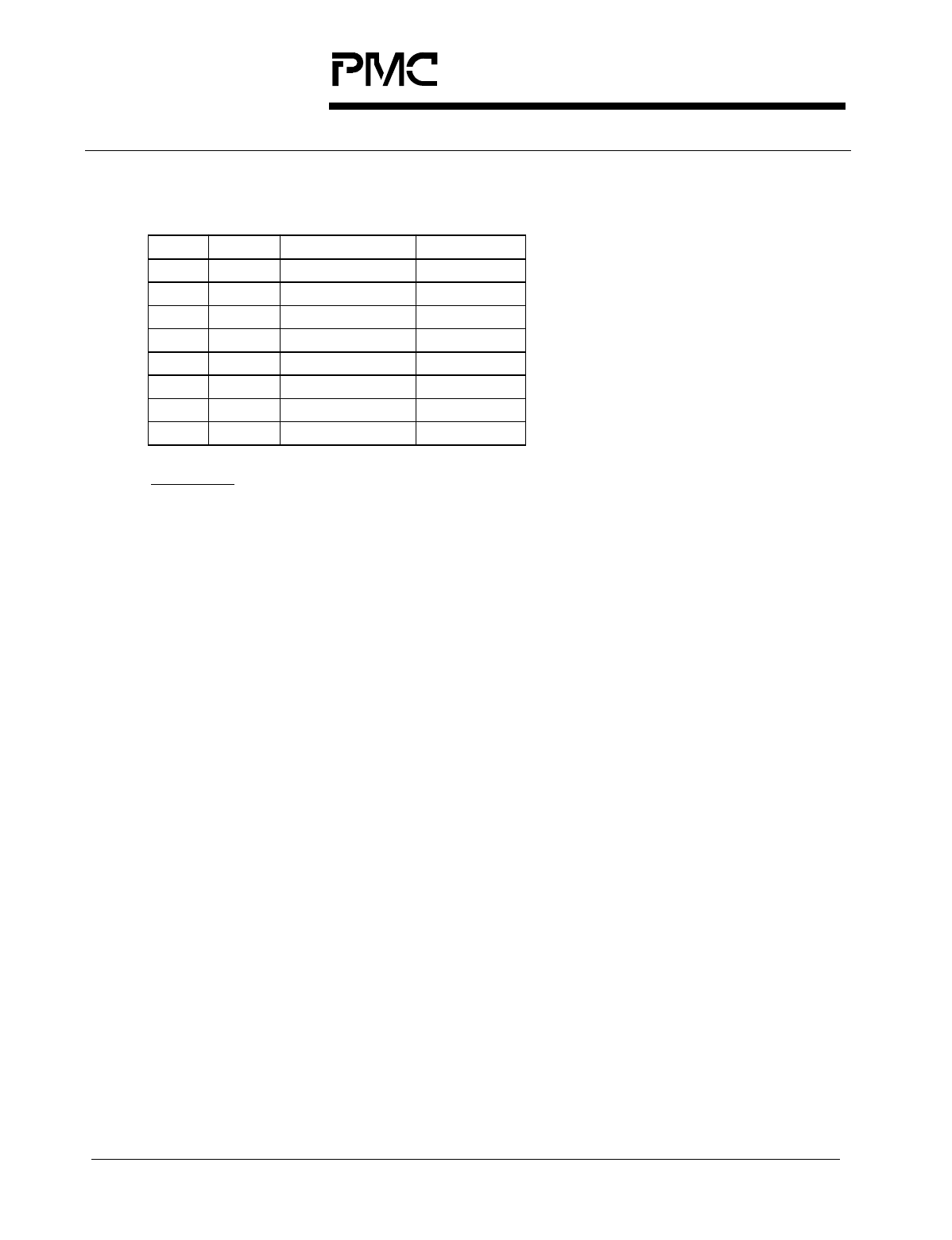

Register 0x1C: RLOP Line BIP-24 MSB

Bit Type Function Default

Bit 7 Unused X

Bit 6 Unused X

Bit 5 Unused X

Bit 4 Unused X

Bit 3 R LBE[19] X

Bit 2 R LBE[18] X

Bit 1 R LBE[17] X

Bit 0 R LBE[16] X

LBE[19:0]

Bits LBE[19:0] represent the number of line BIP-24 errors (individual or block)

that have been detected since the last time the error count was polled. The

error count is polled by writing to any of the RLOP Line BIP Registers or Line

FEBE Register addresses. Such a write transfers the internally accumulated

error count to the Line BIP Registers within approximately 7 µs and

simultaneously resets the internal counter to begin a new cycle of error

accumulation.

The count can also be polled by writing to the

S/UNI-QUAD Channel Reset

and Monitoring Update register (0x05)

. Writing to register 0x05 simultaneously

loads all the performance meter registers in the RSOP, RLOP, RPOP, RXCP

and TXCP blocks.