S/UNI-QUAD

PMC-Sierra, Inc.

PM5349 S/UNI-QUAD

DATASHEET

PMC-971239 ISSUE 6 SATURN USER NETWORK INTERFACE (155-QUAD)

Proprietary and Confidential to PMC-Sierra, Inc., and for its Customers’ Internal Use

175

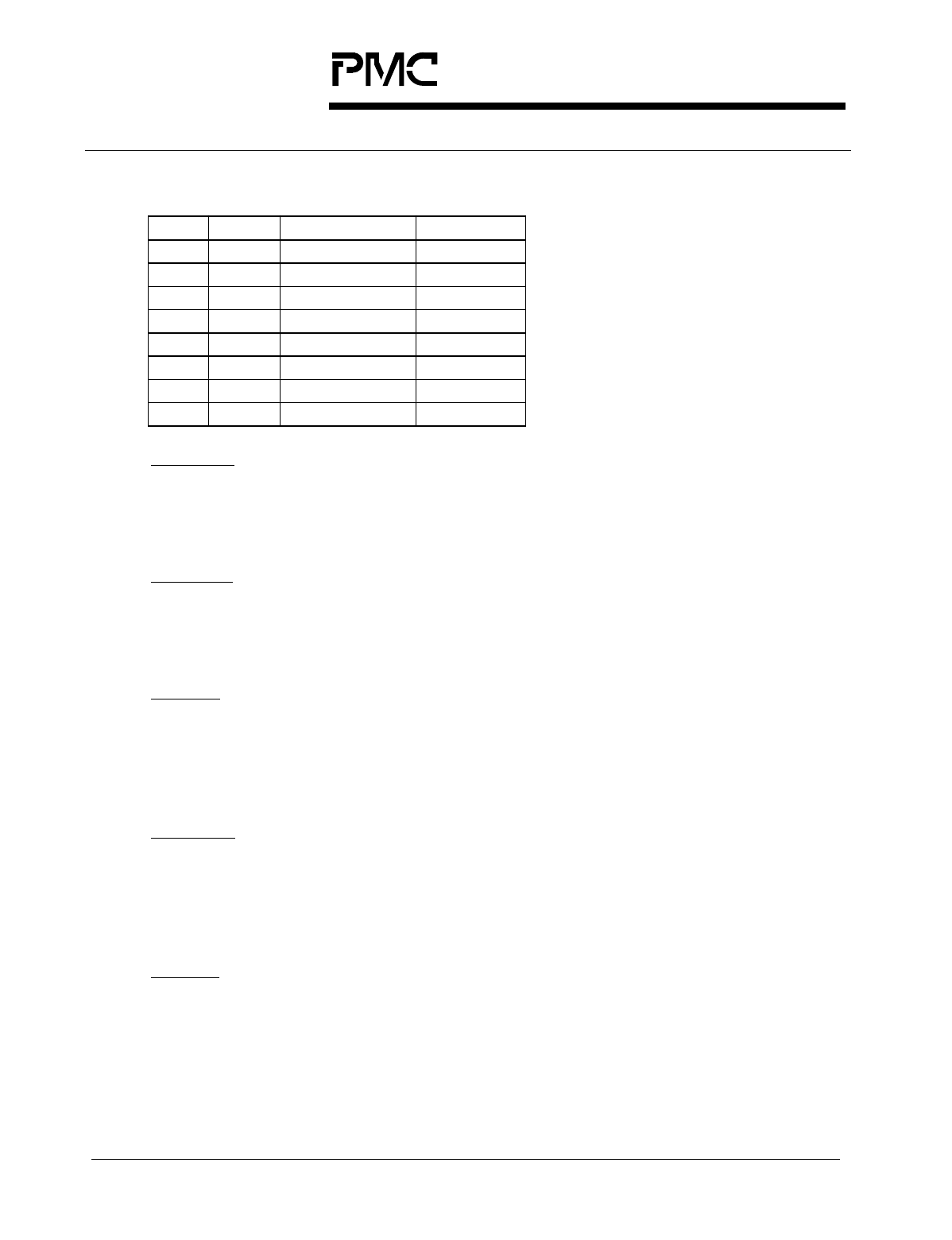

Register 0xE0: RASE Interrupt Enable

Bit Type Function Default

Bit 7 R/W PSBFE 0

Bit 6 R/W COAPSE 0

Bit 5 R/W Z1/S1E 0

Bit 4 R/W SFBERE 0

Bit 3 R/W SDBERE 0

Bit 2 R/W Unused X

Bit 1 R/W Unused X

Bit 0 R/W Unused X

SDBERE:

The SDBERE bit is the interrupt enable for the signal degrade threshold

alarm. When SDBERE is a logic one, an interrupt is generated when the SD

alarm is declared or removed.

SFBERE:

The SFBERE bit is the interrupt enable for the signal fail threshold alarm.

When SFBERE is a logic one, an interrupt is generated when the SF alarm is

declared or removed.

Z1/S1E:

The Z1/S1 interrupt enable is an interrupt mask for changes in the received

synchronization status. When Z1/S1E is a logic one, an interrupt is generated

when a new synchronization status message is extracted into the Receive

Z1/S1 register.

COAPSE:

The COAPS interrupt enable is an interrupt mask for changes in the received

APS code. When COAPSE is a logic one, an interrupt is generated when a

new K1/K2 code value is extracted into the RASE Receive K1 and RASE

Receive K2 registers.

PSBFE:

The PSBF interrupt enable is an interrupt mask for protection switch byte

failure alarms. When PSBFE is a logic one, an interrupt is generated when

PSBF is declared or removed.