S/UNI-QUAD

PMC-Sierra, Inc.

PM5349 S/UNI-QUAD

DATASHEET

PMC-971239 ISSUE 6 SATURN USER NETWORK INTERFACE (155-QUAD)

Proprietary and Confidential to PMC-Sierra, Inc., and for its Customers’ Internal Use

89

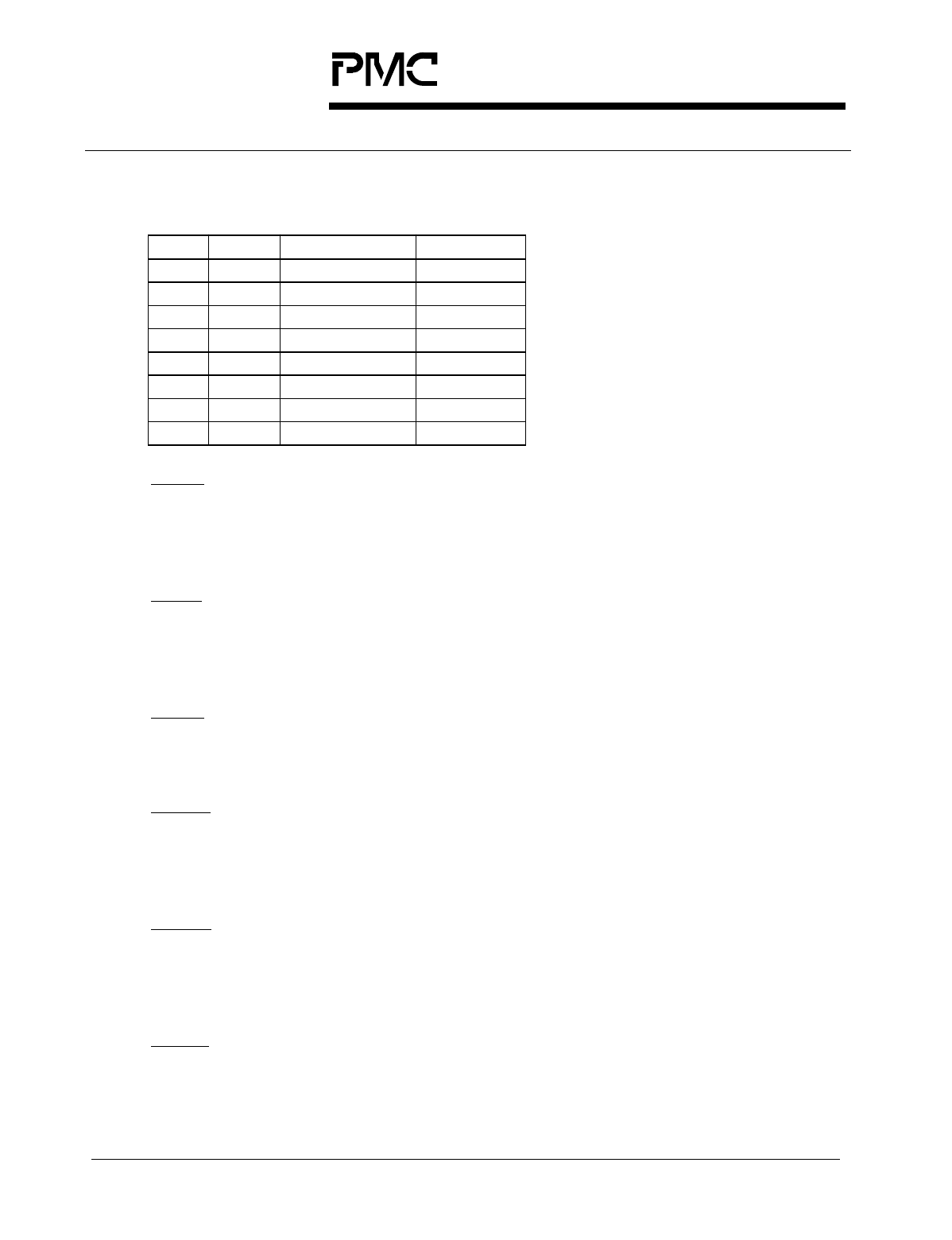

Register 0x19: RLOP Interrupt Enable/Interrupt Status

Bit Type Function Default

Bit 7 R/W FEBEE 0

Bit 6 R/W BIPEE 0

Bit 5 R/W LAISE 0

Bit 4 R/W LRDIE 0

Bit 3 R FEBEI X

Bit 2 R BIPEI X

Bit 1 R LAISI X

Bit 0 R LRDII X

LRDII:

The LRDII bit is the line far end receive failure interrupt status bit. LRDII is set

high when a change in the line RDI state occurs. This bit is cleared when this

register is read.

LAISI:

The LAISI bit is the line AIS interrupt status bit. LAISI is set high when a

change in the line AIS state occurs. This bit is cleared when this register is

read.

BIPEI:

The BIPEI bit is the line BIP interrupt status bit. BIPEI is set high when a line

layer (B2) bit error is detected. This bit is cleared when this register is read.

FEBEI:

The FEBEI bit is the line far end block error interrupt status bit. FEBEI is set

high when a line layer FEBE (M1) is detected. This bit is cleared when this

register is read.

LRDIE:

The LRDIE bit is an interrupt enable for the line remote defect indication

alarm. When LRDIE is set to logic one, an interrupt is generated when line

RDI changes state.

LAISE:

The LAISE bit is an interrupt enable for line AIS. When LAISE is set to logic

one, an interrupt is generated when line AIS changes state.