S/UNI-QUAD

PMC-Sierra, Inc.

PM5349 S/UNI-QUAD

DATASHEET

PMC-971239 ISSUE 6 SATURN USER NETWORK INTERFACE (155-QUAD)

Proprietary and Confidential to PMC-Sierra, Inc., and for its Customers’ Internal Use

87

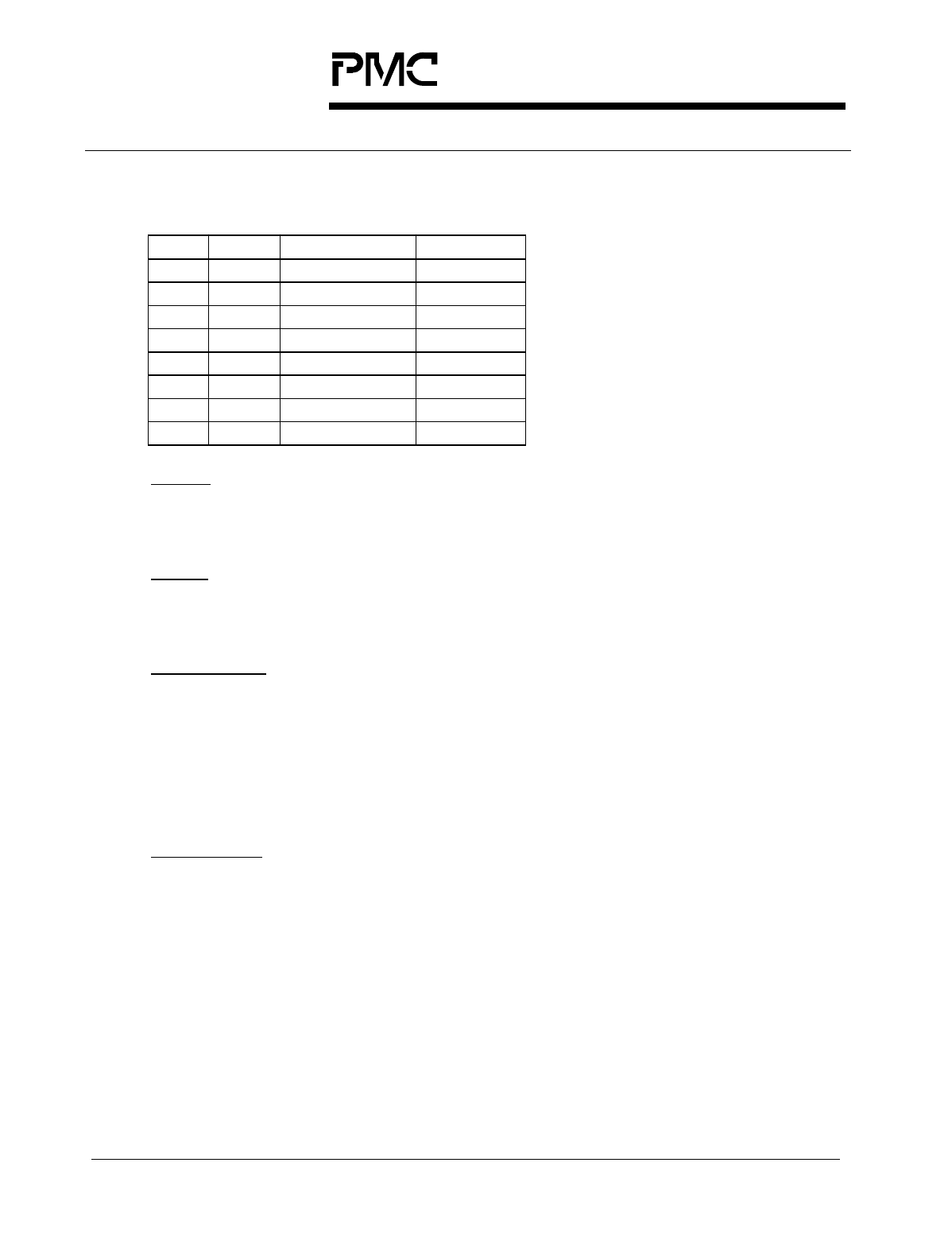

Register 0x18: RLOP Control/Status

Bit Type Function Default

Bit 7 R/W BIPWORD 0

Bit 6 R/W ALLONES 0

Bit 5 R/W AISDET 0

Bit 4 R/W LRDIDET 0

Bit 3 R/W BIPWORDO 0

Bit 2 R/W FEBEWORD 0

Bit 1 R LAISV X

Bit 0 R LRDIV X

LRDIV:

The LRDIV bit is read to determine the remote defect indication state of the

RLOP. When LRDIV is high, the RLOP has declared line RDI.

LAISV:

The LAISV bit is read to determine the line AIS state of the RLOP. When

LAISV is high, the RLOP has declared line AIS.

FEBEWORD:

The FEBEWORD bit controls the accumulation of FEBEs. When

FEBEWORD is logic one, the FEBE event counter is incremented only once

per frame, whenever one or more FEBE bits occur during that frame. When

FEBEWORD is logic zero, the FEBE event counter is incremented for each

and every FEBE bit that occurs during that frame (the counter can be

incremented up to 24).

BIPWORDO:

The BIPWORDO bit controls the indication of B2 errors reported to the TLOP

block for insertion as FEBEs. When BIPWORDO is logic one, the BIP errors

are indicated once per frame whenever one or more B2 bit errors occur

during that frame. When BIPWORD0 is logic zero, BIP errors are indicated

once for every B2 bit error that occurs during that frame. The accumulation of

B2 error events functions independently and is controlled by the BIPWORD

register bit..