S/UNI-QUAD

PMC-Sierra, Inc.

PM5349 S/UNI-QUAD

DATASHEET

PMC-971239 ISSUE 6 SATURN USER NETWORK INTERFACE (155-QUAD)

Proprietary and Confidential to PMC-Sierra, Inc., and for its Customers’ Internal Use

230

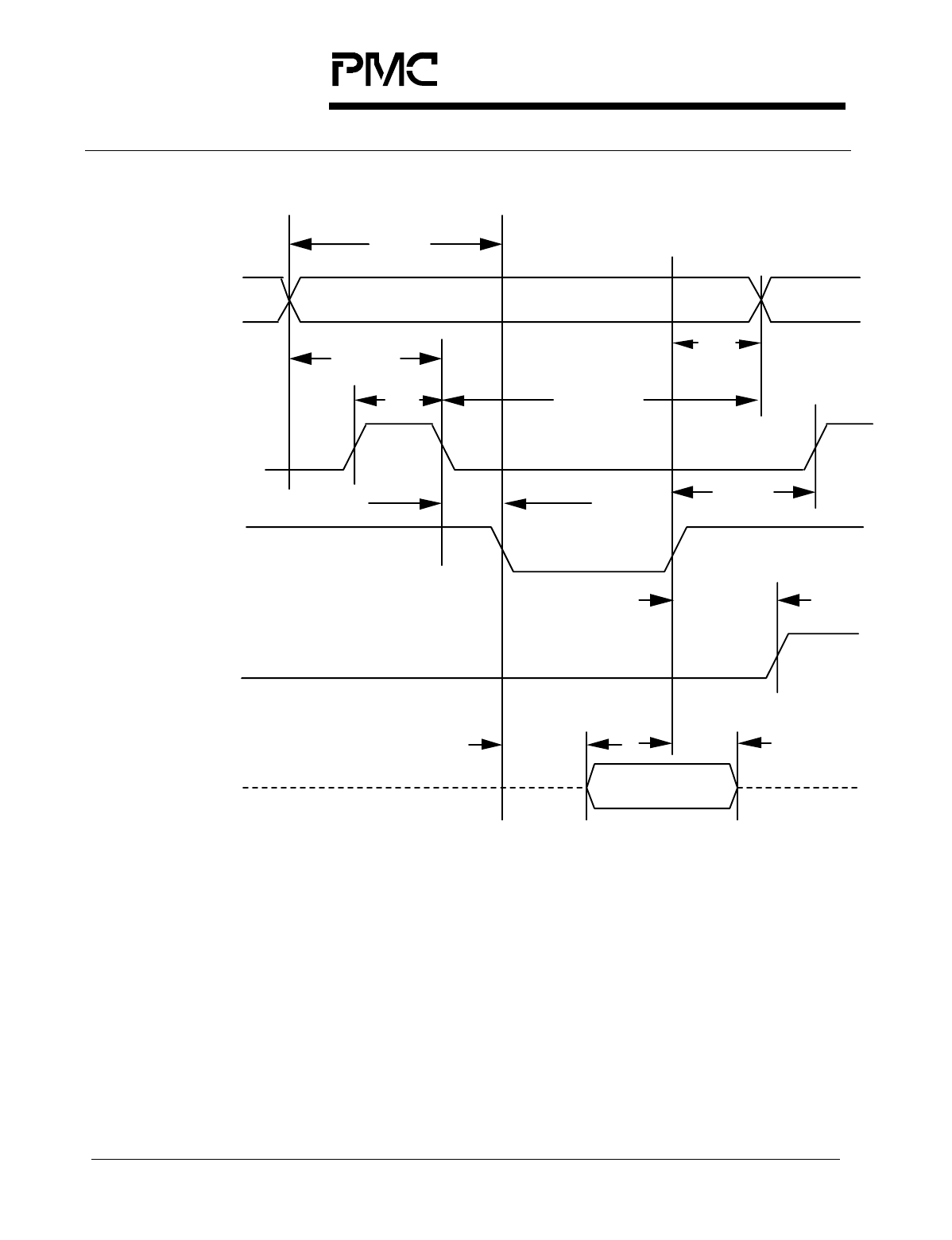

Figure 24: Microprocessor Interface Read Timing

INTB

tZ

INTH

(CSB+RDB)

Valid Data

D[7:0]

tP

RD

tZ

RD

tS

AR

tH

AR

Valid Address

A[10:0]

ALE

tS

ALR

tV

L

tS

LR

tH

ALR

tH

LR

Notes on Microprocessor Interface Read Timing:

1. Output propagation delay time is the time in nanoseconds from the 1.4 Volt

point of the reference signal to the 1.4 Volt point of the output.

2. Maximum output propagation delays are measured with a 100 pF load on the

Microprocessor Interface data bus, (D[7:0]).

3. A valid read cycle is defined as a logical OR of the CSB and the RDB signals.