S/UNI-QUAD

PMC-Sierra, Inc.

PM5349 S/UNI-QUAD

DATASHEET

PMC-971239 ISSUE 6 SATURN USER NETWORK INTERFACE (155-QUAD)

Proprietary and Confidential to PMC-Sierra, Inc., and for its Customers’ Internal Use

136

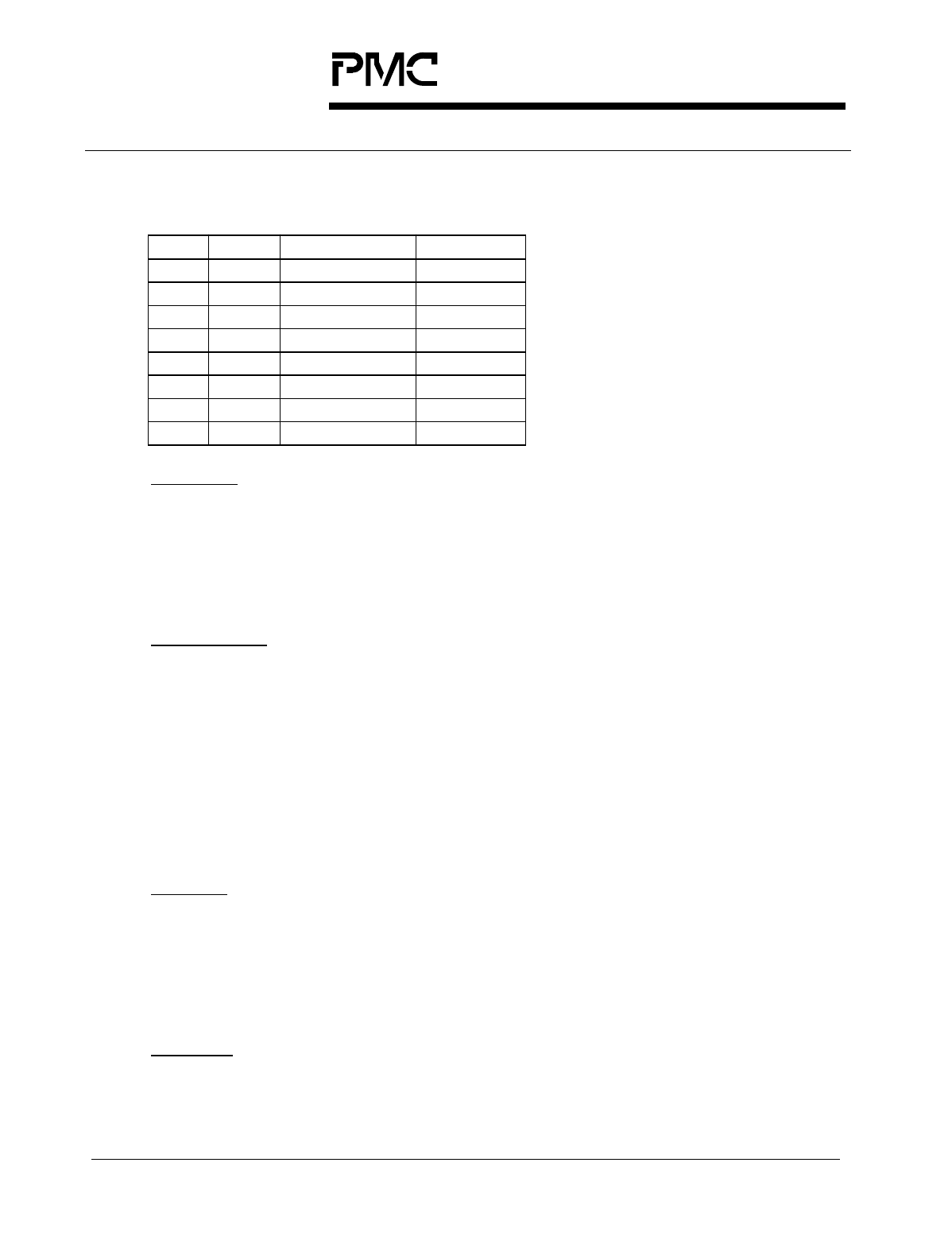

Register 0x62: RXCP FIFO/UTOPIA Control & Config

Bit Type Function Default

Bit 7 R/W RXPTYP 0

Bit 6 Unused X

Bit 5 R/W RCAINV 0

Bit 4 R/W RCALEVEL0 1

Bit 3 Unused X

Bit 2 Unused X

Bit 1 Unused X

Bit 0 R/W FIFORST 0

FIFORST:

The FIFORST bit is used to reset the four-cell receive FIFO. When FIFORST

is set to logic zero, the FIFO operates normally. When FIFORST is set to

logic one, the FIFO is immediately emptied and ignores writes. The FIFO

remains empty and continues to ignore writes until a logic zero is written to

FIFORST.

RCALEVEL0:

The RCA (and DRCA[x]) level 0 bit, RCALEVEL0, determines what output

RCA (and DRCA[x]) indicates when it transitions low. When RCALEVEL0 is

set to logic one, a high-to-low transition on output DRCA[x] and RCA indicates

that the receive FIFO is empty (DRCA[x] and RCA, if polled, will de-assert on

the rising RFCLK edge after Payload word 24 is output. When RCALEVEL0

is set to logic zero, a high-to-low transition on output DRCA[x] and RCA, if

polled, indicates that the receive FIFO is near empty. DRCA[x] and RCA, if

polled, will de-assert on the rising RFCLK edge after Payload byte 19 is

output.

RCAINV:

The RCAINV bit inverts the polarity of the DRCA[x] and RCA output signal.

When RCAINV is a logic one, the polarity of DRCA[x] and RCA is inverted

(DRCA[x] and RCA at logic zero means there is a receive cell available to be

read). When RCAINV is a logic zero, the polarity of RCA and DRCA[x] is not

inverted.

RXPTYP:

The RXPTYP bit selects even or odd parity for output RPRTY. When set to

logic one, output RPRTY is the even parity bit for outputs RDAT[15:0]. When