S/UNI-QUAD

PMC-Sierra, Inc.

PM5349 S/UNI-QUAD

DATASHEET

PMC-971239 ISSUE 6 SATURN USER NETWORK INTERFACE (155-QUAD)

Proprietary and Confidential to PMC-Sierra, Inc., and for its Customers’ Internal Use

223

14

FUNCTIONAL TIMING

All functional timing diagrams assume that polarity control is not being applied to

input and output data and clock lines (i.e. polarity control bits in the S/UNI-QUAD

registers are set to their default states).

14.1

ATM Utopia Level 2 System Interface

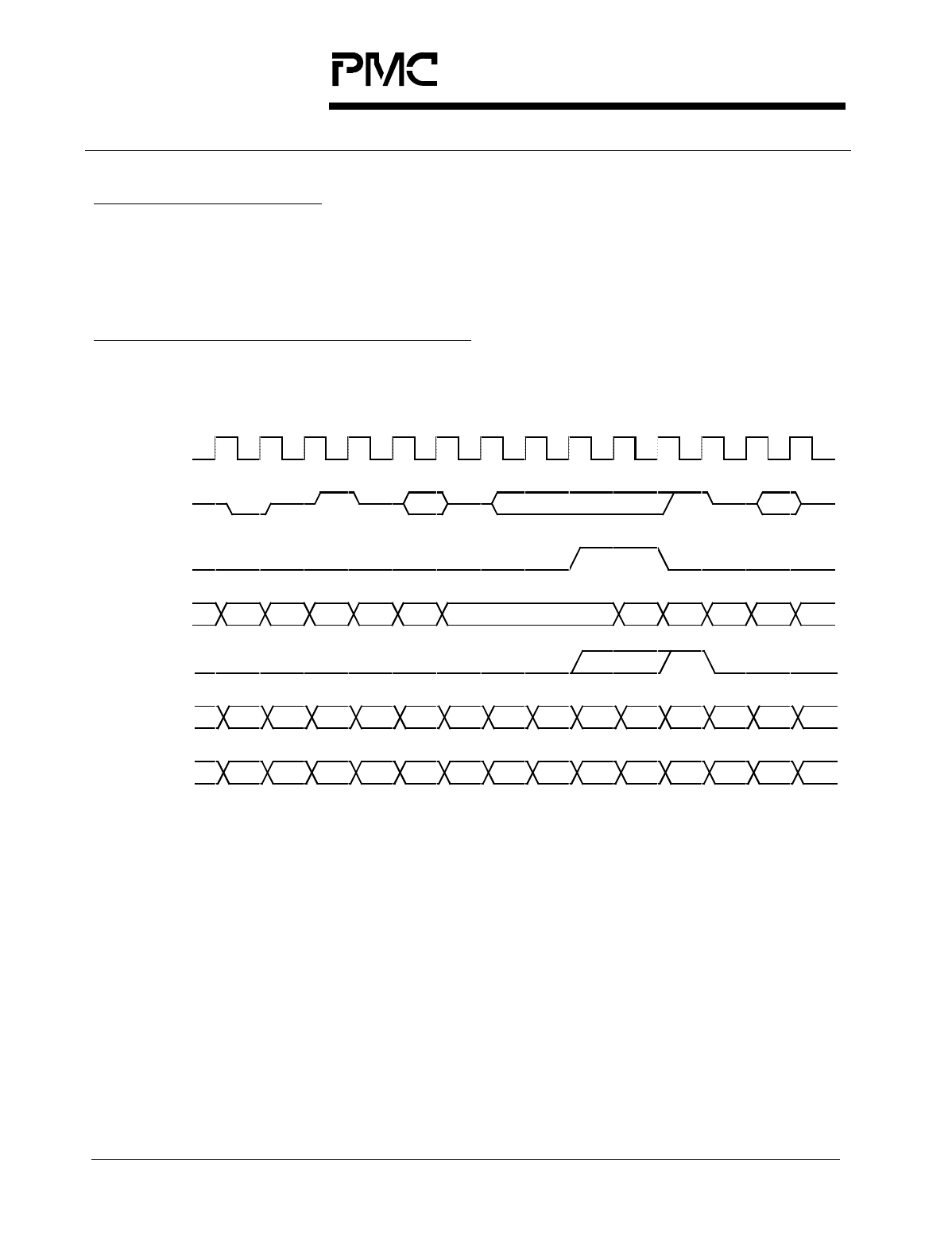

Figure 22: Multi-PHY Polling and Addressing Transmit Cell Interface

TCA

TSOC

TDAT[15:0]

TPRTY

W

(

n-6

)

W

(

n-5

)

W1 W2 W3W

(

n-4

)

W

(

n-3

)

W

(

n-2

)

W

(

n-1

)

W

(

n

)

W

(

n-7

)

W4X X

TFCLK

TENB

TADR[4:0]

CA

(

A

)

CA

(

B

)

CA

(

C

)

CA

(

B

)

A B 1Fh C 1Fh B 1Fh A 1Fh C 1Fh

CA

(

A

)

X

X

Figure 66 is an example of the multi-PHY polling and selection sequence

supported by the S/UNI-QUAD. "A", "B", and "C" represent any arbitrary address

values of PHY devices which may be occupied by the S/UNI-QUAD. The ATM

Layer device is not restricted in its polling order. The PHY associated with

address "A" indicates it cannot accept a cell, but PHY "B" indicates it is willing to

accept a cell. As a result, the ATM Layer places address "B" on TADR[4:0] the

cycle before TENB is asserted to select PHY "B" as the next cell destination. In

this example, the PHY "C" status is ignored. The ATM Layer device is not

constrained to select the latest PHY polled. As soon as the cell transfer is

started, the polling process may be restarted.