S/UNI-QUAD

PMC-Sierra, Inc.

PM5349 S/UNI-QUAD

DATASHEET

PMC-971239 ISSUE 6 SATURN USER NETWORK INTERFACE (155-QUAD)

Proprietary and Confidential to PMC-Sierra, Inc., and for its Customers’ Internal Use

195

DBCTRL:

The DBCTRL bit is used to pass control of the data bus drivers to the CSB

pin. When the DBCTRL bit is set to logic one and either IOTST or PMCTST

are logic one, the CSB pin controls the output enable for the data bus. While

the DBCTRL bit is set, holding the CSB pin high causes the S/UNI-QUAD to

drive the data bus and holding the CSB pin low tri-states the data bus. The

DBCTRL bit overrides the HIZDATA bit. The DBCTRL bit is used to measure

the drive capability of the data bus driver pads.

PMCTST:

The PMCTST bit is used to configure the S/UNI-QUAD for PMC's

manufacturing tests. When PMCTST is set to logic one, the S/UNI-QUAD

microprocessor port becomes the test access port used to run the PMC

"canned" manufacturing test vectors. The PMCTST bit is logically "ORed"

with the IOTST bit, and can be cleared by setting CSB to logic one or by

writing logic zero to the bit.

PMCATST:

The PMCATST bit is used to configure the analog portion of the S/UNI-QUAD

for PMC's manufacturing tests.

Reserved:

The reserved bit must be programmed to logic one for proper operation.

12.2

Test Mode 0 Details

In test mode 0, the S/UNI-QUAD allows the logic levels on the device inputs to be

read through the microprocessor interface and allows the device outputs to be

forced to either logic level through the microprocessor interface. The IOTST bit in

the Master Test register must be set to logic one to access the device I/O.

To enable test mode 0, the IOTST bit in the Master Test register is set to logic one

and the following addresses must be written with 00H: TBD.

Reading the following address locations returns the values on the indicated

inputs:

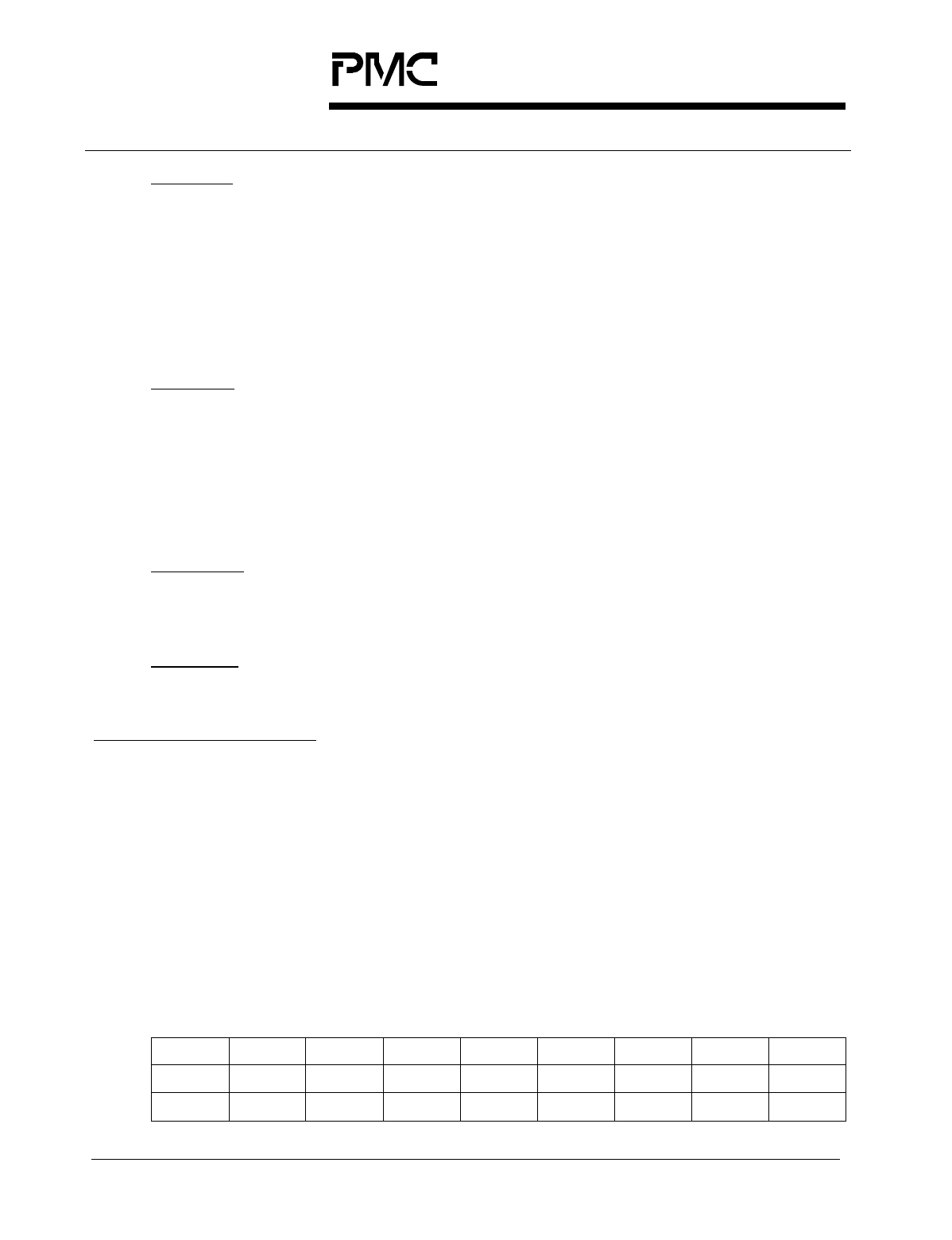

Table 7: Test Mode 0 Read Locations

Addr Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

08H

0FH