S/UNI-QUAD

PMC-Sierra, Inc.

PM5349 S/UNI-QUAD

DATASHEET

PMC-971239 ISSUE 6 SATURN USER NETWORK INTERFACE (155-QUAD)

Proprietary and Confidential to PMC-Sierra, Inc., and for its Customers’ Internal Use

194

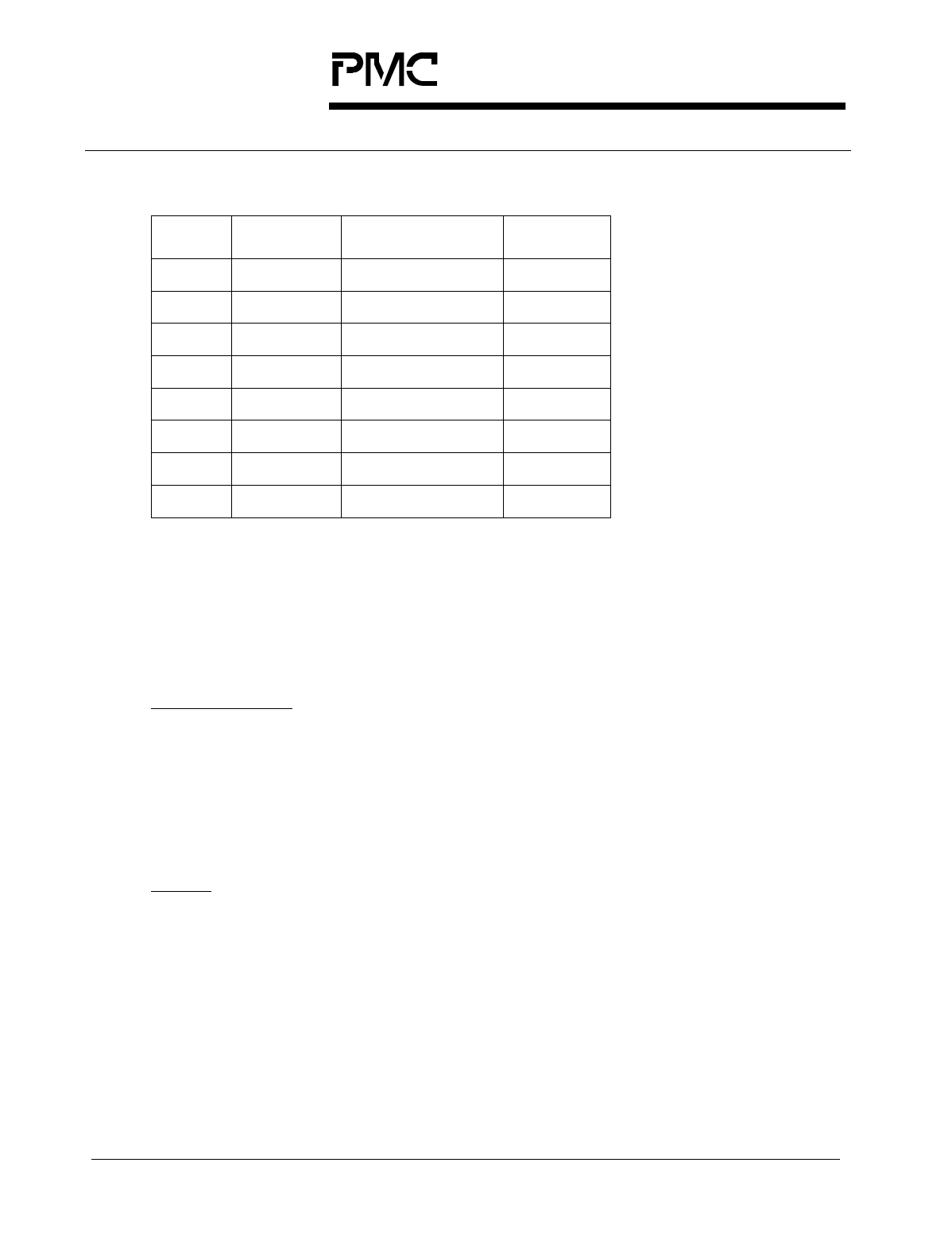

Register 0x400: Master Test

Bit Type Function Default

Bit 7

Unused X

Bit 6

W Reserved X

Bit 5

WPMCATSTX

Bit 4

WPMCTSTX

Bit 3

WDBCTRL0

Bit 2

R/W IOTST 0

Bit 1

WHIZDATA0

Bit 0

R/W HIZIO 0

This register is used to enable S/UNI-QUAD test features. All bits, except

PMCTST, PMCATST and BYPASS are reset to zero by a reset of the

S/UNI-QUAD using either the RSTB input or the Master Reset register. PMCTST

and BYPASS are reset when CSB is logic one. PMCATST is reset when both

CSB is high and RSTB is low. PMCTST, PMCATST and BYPASS can also be

reset by writing a logic zero to the corresponding register bit.

HIZIO, HIZDATA:

The HIZIO and HIZDATA bits control the tri-state modes of the S/UNI-QUAD .

While the HIZIO bit is a logic one, all output pins of the S/UNI-QUAD except

the data bus and output TDO are held tri-state. The microprocessor interface

is still active. While the HIZDATA bit is a logic one, the data bus is also held in

a high-impedance state which inhibits microprocessor read cycles. The

HIZDATA bit is overridden by the DBCTRL bit.

IOTST:

The IOTST bit is used to allow normal microprocessor access to the test

registers and control the test mode in each TSB block in the S/UNI-QUAD for

board level testing. When IOTST is a logic one, all blocks are held in test

mode and the microprocessor may write to a block's test mode 0 registers to

manipulate the outputs of the block and consequentially the device outputs

(refer to the "Test Mode 0 Details" in the "Test Features" section).