S/UNI-QUAD

PMC-Sierra, Inc.

PM5349 S/UNI-QUAD

DATASHEET

PMC-971239 ISSUE 6 SATURN USER NETWORK INTERFACE (155-QUAD)

Proprietary and Confidential to PMC-Sierra, Inc., and for its Customers’ Internal Use

170

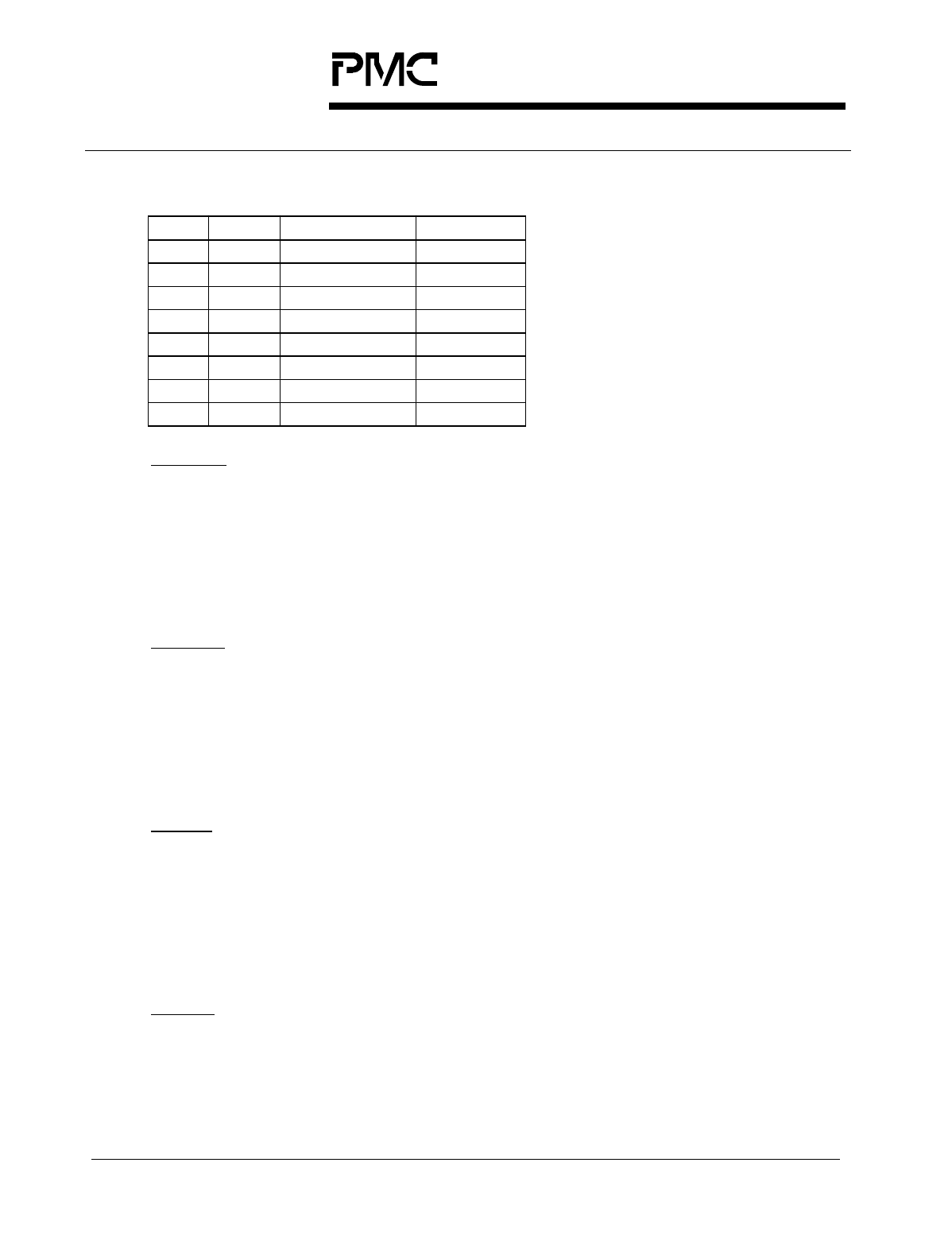

Register 0x94: S/UNI-QUAD Channel Receive Line AIS Control

Bit Type Function Default

Bit 7 R/W SDINS 0

Bit 6 R/W SFINS 0

Bit 5 R/W LOFINS 1

Bit 4 R/W LOSINS 1

Bit 3 R/W Reserved 0

Bit 2 R/W Reserved 0

Bit 1 Unused X

Bit 0 R/W Reserved 0

LOSINS:

This bit is active only when the ALLONES bit in the RLOP Control/Status

register is set high; it is ignored if the ALLONES bit is set low. The LOSINS bit

enables the insertion of line AIS in the receive direction upon the declaration

of loss of signal (LOS). If LOSINS is a logic one, line AIS is inserted into the

SONET/SDH frame when LOS is declared. Line AIS is terminated when LOS

is removed.

LOFINS:

This bit is active only when the ALLONES bit in the RLOP Control/Status

register is set high; it is ignored if the ALLONES bit is set low. The LOFINS bit

enables the insertion of line AIS in the receive direction upon the declaration

of loss of frame (LOF). If LOSINS is a logic one, line AIS is inserted into the

SONET/SDH frame when LOS is declared. Line AIS is terminated when LOS

is removed.

SFINS:

This bit is active only when the ALLONES bit in the RLOP Control/Status

register is set high; it is ignored if the ALLONES bit is set low. The SFINS bit

enables the insertion of line AIS in the receive direction upon the declaration

of signal fail (SF). If SFINS is a logic one, line AIS is inserted into the

SONET/SDH frame when SF is declared. Line AIS is terminated when SF is

removed.

SDINS:

This bit is active only when the ALLONES bit in the RLOP Control/Status

register is set high; it is ignored if the ALLONES bit is set low. The SDINS bit

enables the insertion of line AIS in the receive direction upon the declaration

of signal degrade (SD). If SDINS is a logic one, line AIS is inserted into the