S/UNI-QUAD

PMC-Sierra, Inc.

PM5349 S/UNI-QUAD

DATASHEET

PMC-971239 ISSUE 6 SATURN USER NETWORK INTERFACE (155-QUAD)

Proprietary and Confidential to PMC-Sierra, Inc., and for its Customers’ Internal Use

19

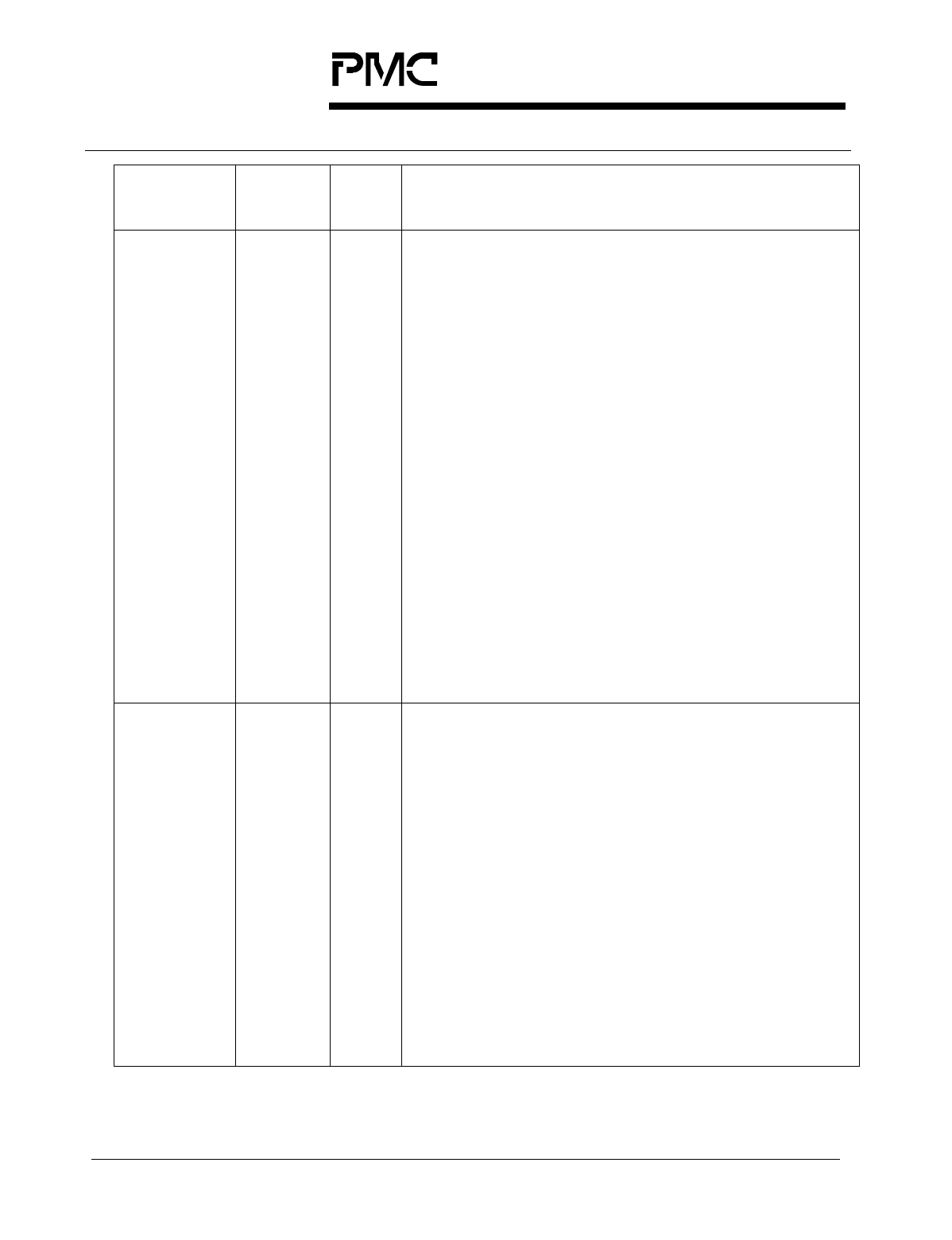

Pin Name Type Pin

No.

Function

DTCA[4]

DTCA[3]

DTCA[2]

DTCA[1]

Output K22

K23

L20

L21

UTOPIA Direct Transmit Cell Available (DTCA[4:1]).

These output signals provide direct status indication

of when a cell is available in the transmit FIFO for

the corresponding port. When high, DTCA indicates

that the corresponding transmit FIFO is not full and

a complete cell may be written. When DTCA goes

low, it can be configured to indicate either that the

corresponding transmit FIFO is near full or that the

corresponding transmit FIFO is full. DTCA will

transition low on the rising edge of TFCLK after the

Payload word 19 (TCALEVEL0=0) or 23

(TCALEVEL0=1) is sampled if the PHY being polled

is the same as the PHY in use. To reduce FIFO

latency, the FIFO depth at which DTCA indicates

"full" can be set to one, two, three or four cells. Note

that regardless of what fill level DTCA is set to

indicate "full" at, the transmit cell processor can

store 4 complete cells

DTCA[4:1] are updated on the rising edge of

TFCLK.

RDAT[15]

RDAT[14]

RDAT[13]

RDAT[12]

RDAT[11]

RDAT[10]

RDAT[9]

RDAT[8]

RDAT[7]

RDAT[6]

RDAT[5]

RDAT[4]

RDAT[3]

RDAT[2]

RDAT[1]

RDAT[0]

Output U23

U22

T20

U21

V22

W23

U20

V21

W22

Y23

W21

Y22

AA23

W20

Y21

AA20

UTOPIA Receive Cell Data Bus (RDAT[15:0]).

This data bus carries the ATM cells that are read

from the receive FIFO selected by RADR[4:0].

RDAT[15:0] is tri-stated when RENB is high.

RDAT[15:0] is tristated when RENB is high.

RDAT[15:0] is also tristated when either the null-

PHY address (0x1F) or an address not matching

the address space is latched from the RADR[4:0]

inputs when RENB is high.

RDAT[15:0] is updated on the rising edge of

RFCLK.