S/UNI-QUAD

PMC-Sierra, Inc.

PM5349 S/UNI-QUAD

DATASHEET

PMC-971239 ISSUE 6 SATURN USER NETWORK INTERFACE (155-QUAD)

Proprietary and Confidential to PMC-Sierra, Inc., and for its Customers’ Internal Use

178

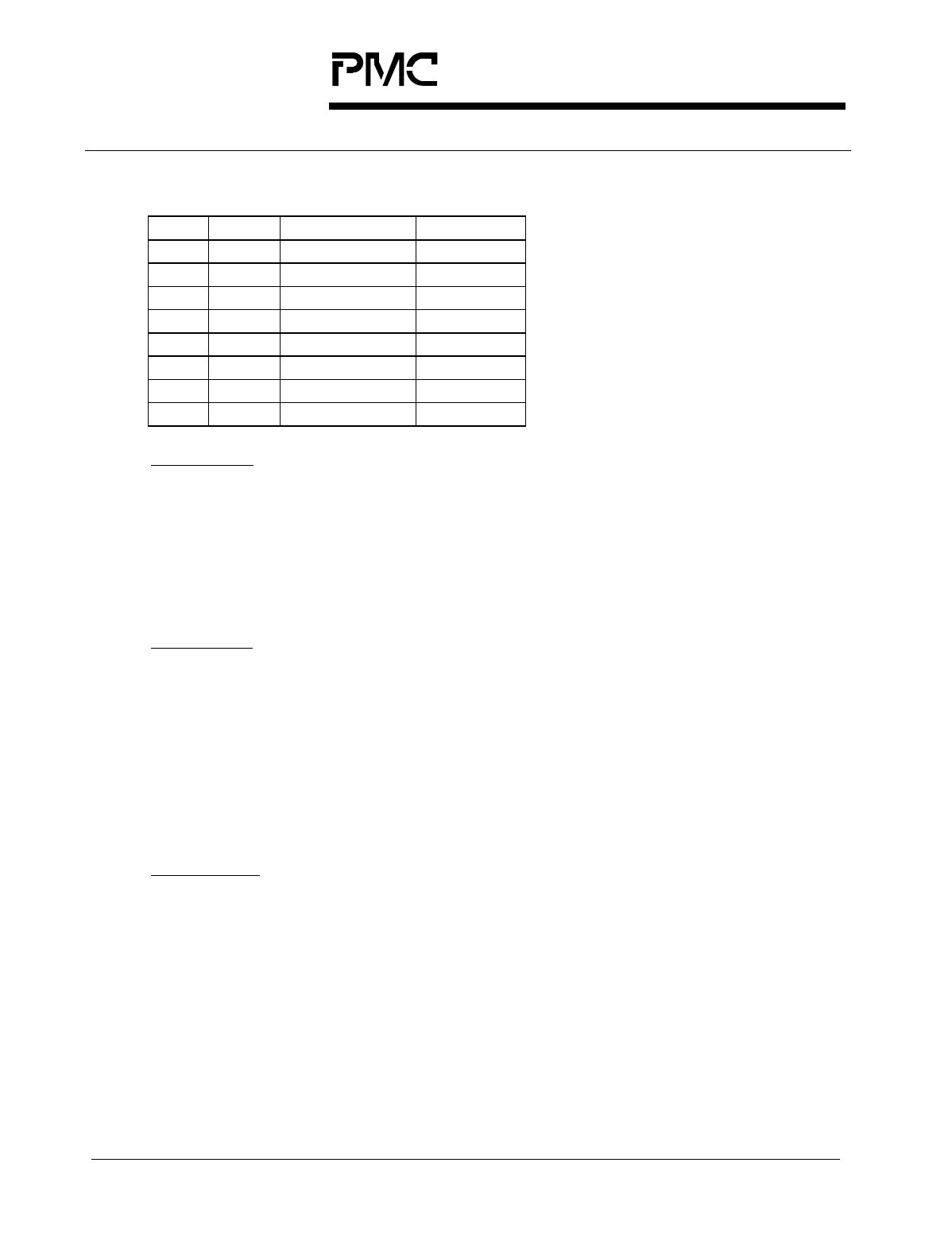

Register 0xE2: RASE Configuration/Control

Bit Type Function Default

Bit 7 R/W Z1/S1_CAP 0

Bit 6 R/W SFBERTEN 0

Bit 5 R/W SFSMODE 0

Bit 4 R/W SFCMODE 0

Bit 3 R/W SDBERTEN 0

Bit 2 R/W SDSMODE 0

Bit 1 R/W SDCMODE 0

Bit 0 R/W Unused X

SDCMODE:

The SDCMODE alarm bit selects the RASE window size to use for clearing

the SD alarm. When SDCMODE is a logic zero the RASE clears the SD alarm

using the same window size used for declaration. When SDCMODE is a logic

one the RASE clears the SD alarm using a window size that is 8 times longer

than the alarm declaration window size. The declaration window size is

determined by the RASE SD Accumulation Period registers.

SDSMODE:

The SDSMODE bit selects the RASE saturation mode. When SDSMODE is a

logic zero the RASE limits the number of B2 errors accumulated in one frame

period to the RASE SD Saturation Threshold register value. When SDSMODE

is a logic one the RASE limits the number of B2 errors accumulated in one

window subtotal accumulation period to the RASE SD Saturation Threshold

register value. Note that the number of frames in a window subtotal

accumulation period is determined by the RASE SD Accumulation Period

register value.

SDBERTEN:

The SDBERTEN bit selects automatic monitoring of line bit error rate

threshold events by the RASE. When SDBERTEN is a logic one, the RASE

continuously monitors line BIP errors over a period defined in the RASE

configuration registers. When SDBERTEN is a logic zero, the RASE BIP

accumulation logic is disabled, and the RASE logic is reset to the declaration

monitoring state.

All RASE accumulation period and threshold registers should be set up before

SDBERTEN is written.