S/UNI-QUAD

PMC-Sierra, Inc.

PM5349 S/UNI-QUAD

DATASHEET

PMC-971239 ISSUE 6 SATURN USER NETWORK INTERFACE (155-QUAD)

Proprietary and Confidential to PMC-Sierra, Inc., and for its Customers’ Internal Use

153

Register 0x81: TXCP Configuration 2

Bit Type Function Default

Bit 7 Unused X

Bit 6 Unused X

Bit 5 Unused X

Bit 4 R/W TCAINV 0

Bit 3 R/W FIFODP[1] 0

Bit 2 R/W FIFODP[0] 0

Bit 1 R/W DHCS 0

Bit 0 R/W HCSCTLEB 0

HCSCTLEB:

The active low HCS control enable, HCSCTLEB bit enables the XORing of the

HCS Control byte with the generated HCS. When set to logic zero, the HCS

Control byte provided in the third word of the 27 word data structure is XORed

with the generated HCS. When set to logic one, XORing is disabled and the

HCS Control byte is ignored.

DHCS:

The DHCS bit controls the insertion of HCS errors for diagnostic purposes.

When DHCS is set to logic one, the HCS octet is inverted prior to insertion in

the synchronous payload envelope. DHCS takes effect unconditionally

regardless of whether a null/unassigned cell is being transmitted or whether

the HCS octet was read from the FIFO. DHCS occurs after any error insertion

caused by the Control Byte in the 27-word data structure.

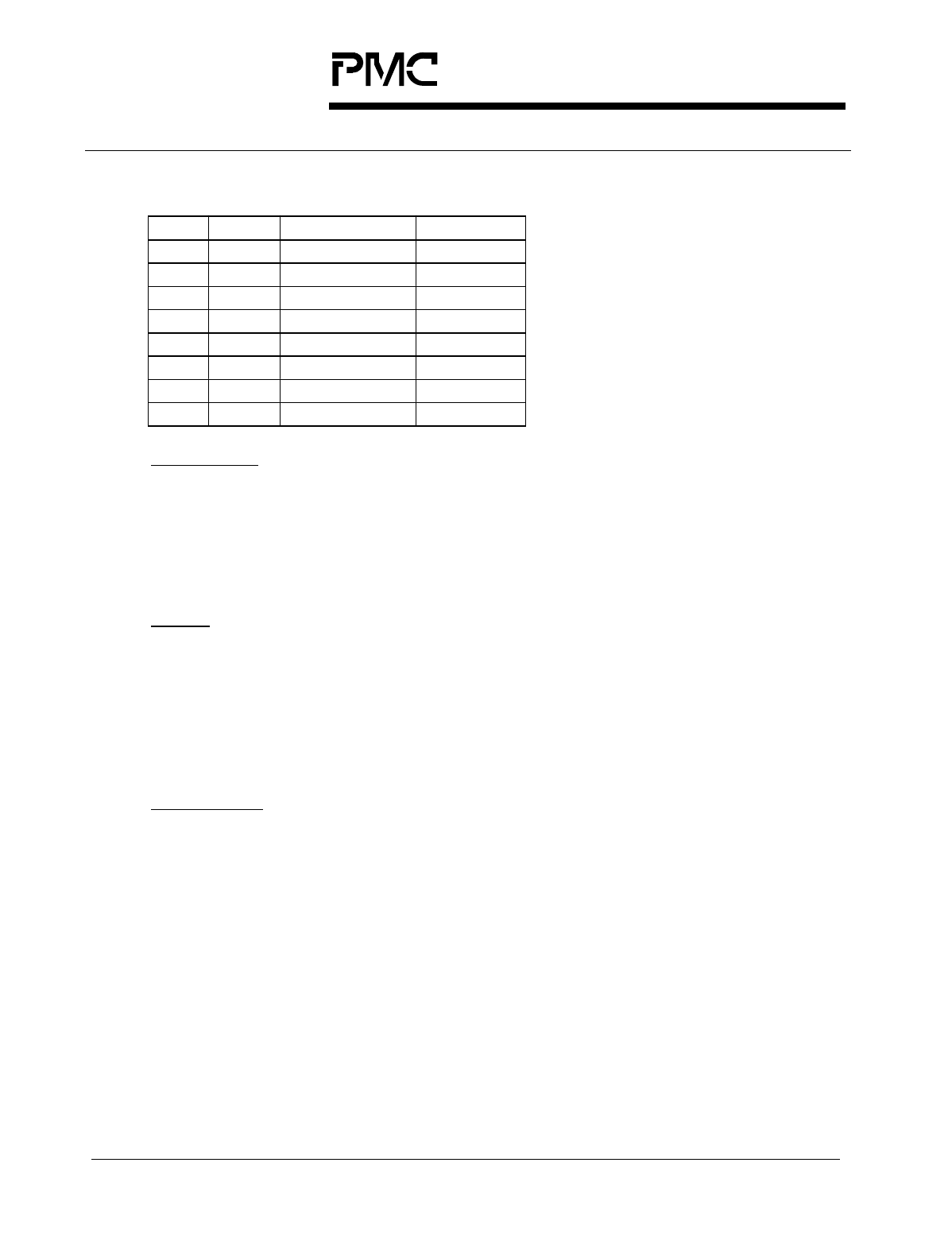

FIFODP[1:0]:

The FIFODP[1:0] bits determine the transmit FIFO cell depth at which TCA

and DTCA[x] de-assert. FIFO depth control may be important in systems

where the cell latency through the TXCP must be minimized. When the FIFO

is filled to the specified depth, the transmit cell available signal, TCA (and

DTCA[x]) is asserted. Note that regardless of what fill level FIFODP[1:0] is

set to, the transmit cell processor can store 4 complete cells. The selectable

FIFO cell depths are shown below: