S/UNI-QUAD

PMC-Sierra, Inc.

PM5349 S/UNI-QUAD

DATASHEET

PMC-971239 ISSUE 6 SATURN USER NETWORK INTERFACE (155-QUAD)

Proprietary and Confidential to PMC-Sierra, Inc., and for its Customers’ Internal Use

140

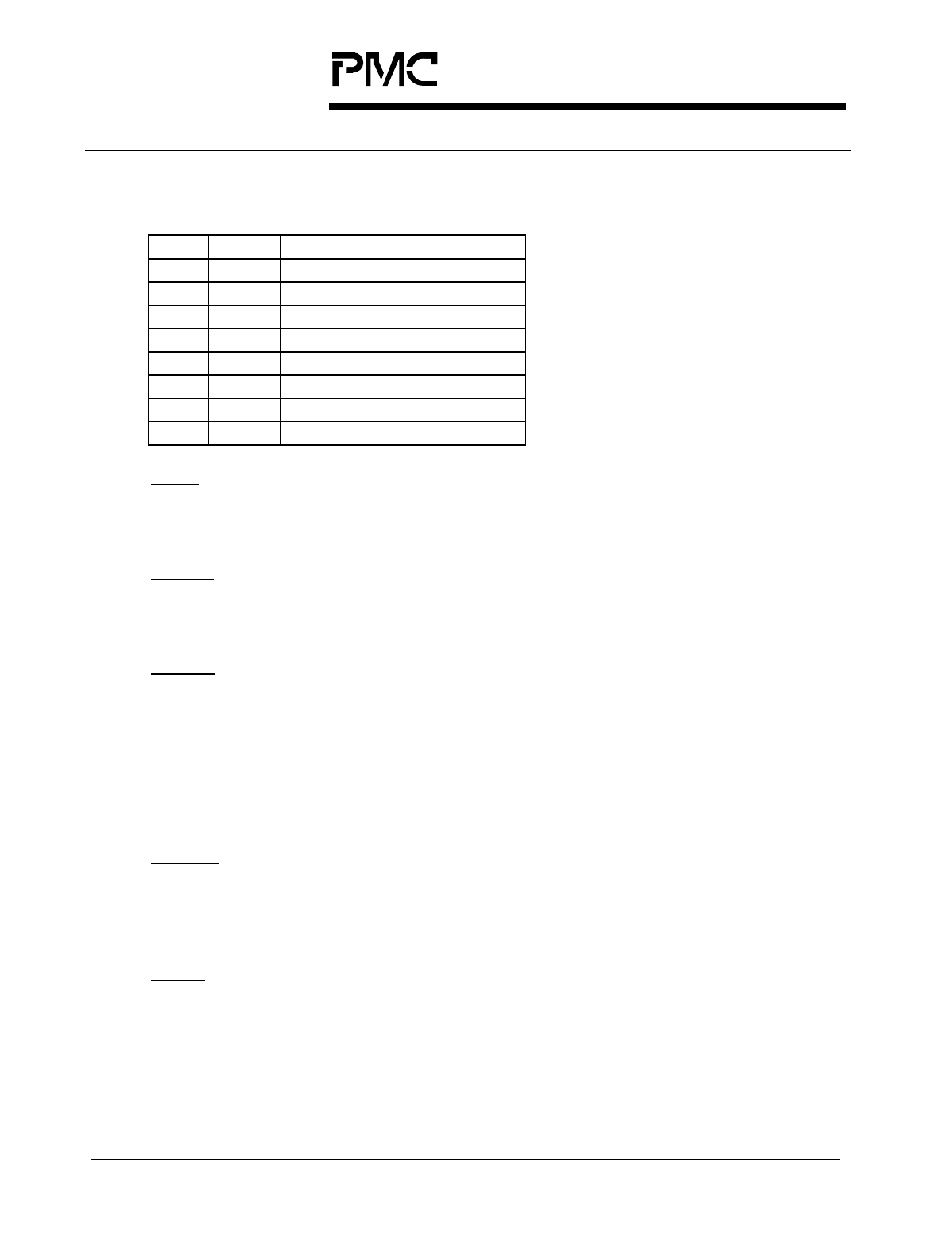

Register 0x64: RXCP Status/Interrupt Status

Bit Type Function Default

Bit 7 R OOCDV X

Bit 6 R LCDV X

Bit 5 Unused X

Bit 4 R OOCDI X

Bit 3 R CHCSI X

Bit 2 R UHCSI X

Bit 1 R FOVRI X

Bit 0 R LCDI X

LCDI:

The LCDI bit is set high when there is a change in the loss of cell delineation

(LCD) state. This bit is reset immediately after a read to this register.

FOVRI:

The FOVRI bit is set to logic one when a FIFO overrun occurs. This bit is

reset immediately after a read to this register.

UHCSI:

The UHCSI bit is set high when an uncorrected HCS error is detected. This

bit is reset immediately after a read to this register.

CHCSI:

The CHCSI bit is set high when a corrected HCS error is detected. This bit is

reset immediately after a read to this register.

OOCDI:

The OOCDI bit is set high when the RXCP enters or exits the SYNC state.

The OOCDV bit indicates whether the RXCP is in the SYNC state or not. The

OOCDI bit is reset immediately after a read to this register.

LCDV:

The LCDV bit gives the Loss of Cell Delineation state. When LCD is logic

one, an out of cell delineation (OCD) defect has persisted for the number of

cells specified in the LCD Count Threshold register. When LCD is logic zero,

no OCD has persisted for the number of cells specified in the LCD Count

Threshold register. The cell time period can be varied by using the LCDC[7:0]

register bits in the RXCP LCD Count Threshold register.