Theory of Operation Chapter 6

VXI-MXI User Manual 6-8 © National Instruments Corporation

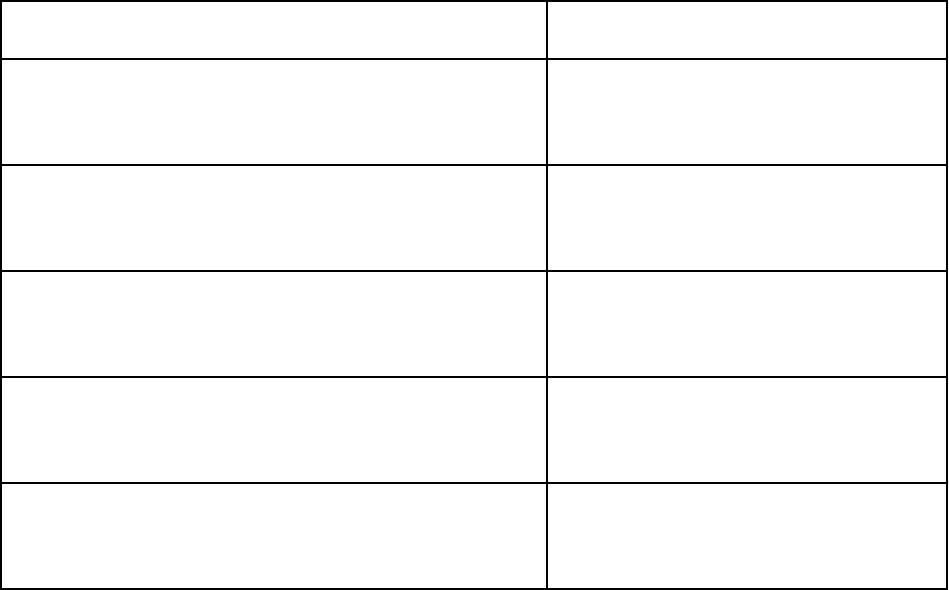

Table 6-3. Transfer Responses for VMEbus Address Modifiers

AM5 AM4 AM3 AM2 AM1 AM0 Transfer Type

HHHHHHA24 supervisory block transfer

HHHHHLA24 supervisory program access

HHHHLHA24 supervisory data access

HHHLHHA24 nonprivileged block transfer

HHHLHLA24 nonprivileged program access

H H H L L H A24 nonprivileged data access

H L H H L H A16 supervisory access

H L H L H L MXIbus transparent IACK cycle

H L H L L H A16 nonprivileged access

LLHHHHA32 supervisory block transfer

LLHHHLA32 supervisory program access

L L H H L H A32 supervisory data access

L L H L H H A32 nonprivileged block transfer

L L H L H L A32 nonprivileged program access

L L H L L H A32 nonprivileged data access

Information specifying the number of bytes and which bytes are involved in a VMEbus transfer

is sent on data strobe lines DS1* and DS0*, address line A01, and the LWORD* line. During

MXIbus transfers, the same information is transferred on the Size line, and Address/Data lines 1

and 0 (AD01 and AD00). The VMEbus transfer size information is converted into MXIbus

transfer size information during a MXIbus master transfer. Table 6-4 compares this information

for the VMEbus and the MXIbus.