Chapter 4 Register Descriptions

© National Instruments Corporation 4-37 VXI-MXI User Manual

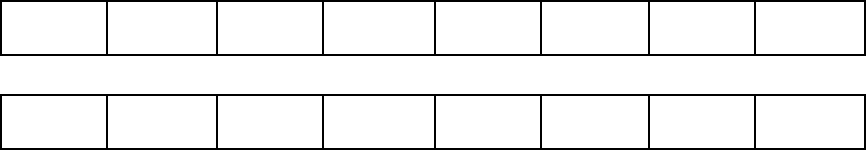

MXIbus IRQ Configuration Register

VXIbus Address: Base Address + 24 (hex)

Attributes: Read/Write

R/W

15 14 13 12 11 10 9

SYSFOU

T

MIRQ7E

N

MIRQ6E

N

MIRQ5E

N

MIRQ4E

N

MIRQ3E

N

MIRQ2E

N

MIRQ1E

N

8

R/W

7 65432

1

SYSFI

N

MIRQ7DI

R

MIRQ6DI

R

MIRQ5DI

R

MIRQ4DI

R

MIRQ3DI

R

MIRQ2DI

R

MIRQ1DI

R

0

This register either maps the MXIbus IRQ line onto a VMEbus IRQ line, or maps a VMEbus

IRQ line onto the MXIbus IRQ line. These bits are cleared on a hard reset.

Bit Mnemonic Description

15r/w SYSFOUT SYSFAIL Output Enable Bit

Setting this bit enables the VXIbus SYSFAIL line to be routed

onto the MXIbus IRQ line. When this bit is cleared, the SYSFAIL

line is not mapped to the MXIbus IRQ line.

14-8r/w MIRQ[7-1]EN MXIbus IRQ Enable Bits

Setting these bits individually enables the corresponding VMEbus

IRQ lines to drive or receive the MXIbus IRQ interrupt line. The

corresponding MIRQDIR bits select whether the MXIbus IRQ

interrupt line is driven or received by the VMEbus IRQ line.

7r/w SYSFIN SYSFAIL Input Enable Bit

Setting this bit enables the MXIbus IRQ line to be driven on the

VMEbus SYSFAIL line. When this bit is cleared, the MXIbus

IRQ line is not mapped onto the SYSFAIL line.

6-0r/w MIRQ[7-1]DIR MXIbus IRQ Direction Bits

When the corresponding MIRQxEN bits are clear, these bits have

no meaning.

When the corresponding MIRQxEN bits are set, these bits control

the routing of the MXIbus IRQ signal. When MIRQxDIR is clear,

the corresponding VMEbus IRQ line drives the MXIbus IRQ line.

If multiple VMEbus IRQ lines are enabled to drive the MXIbus

IRQ line, the selected VMEbus IRQ lines are ORed together and

the result drives the MXIbus IRQ line. If the MIRQxDIR bit is set,

the MXIbus IRQ line drives the corresponding VMEbus IRQ line.