Register Descriptions Chapter 4

VXI-MXI User Manual 4-12 © National Instruments Corporation

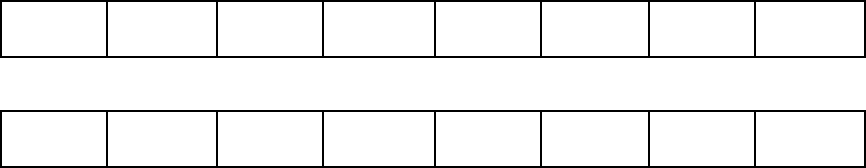

The Logical Address Window Register has the following format when the CMODE bit is set:

R/W

7 65432

1

LALOW7 LALOW6 LALOW5 LALOW4 LALOW3 LALOW2

LALOW1

LALOW0

0

15 14 13 12 11 10 9 8

R/W

LAHIGH7 LAHIGH6 LAHIGH5 LAHIGH4 LAHIGH3 LAHIGH2

LAHIGH1

LAHIGH0

Bit Mnemonic Description

15-8r/w LAHIGH[7-0] Logical Address Window Upper Bound Bits

These bits define the upper limit of the range of MXIbus logical

addresses that map into the VXIbus.

7-0r/w LALOW[7-0] Logical Address Window Lower Bound Bits

These bits define the lower limit of the range of MXIbus logical

addresses that map into the VXIbus.

This register defines the range of MXIbus logical addresses that map into the VXIbus where that

range is:

LAHIGH > range LALOW

The VXIbus logical addresses mapped out of the VXI-MXI are the inverse of this range, that is,

MXIbus logical addresses greater than or equal to the LAHIGH value or less than the LALOW

value.

To map a consecutive range of VXIbus logical addresses out of the VXI-MXI, the lower bound

of the range must be placed in the LAHIGH field and the upper bound in the LALOW field. In

this case, the range of VXIbus logical addresses mapped out of the VXI-MXI is:

LALOW > range LAHIGH

The MXIbus logical addresses mapped into the VXIbus are the inverse of this range, that is,

VXIbus logical addresses greater than or equal to the LALOW value or less than the LAHIGH

value.

The window is disabled whenever LAHIGH = LALOW = 0. All VXIbus logical addresses are

mapped out to the MXIbus when:

FF (hex) (LAHIGH = LALOW) 80 (hex)

All MXIbus logical addresses are mapped into the VXIbus when:

7F (hex) (LAHIGH = LALOW) > 0