Chapter 4 Register Descriptions

© National Instruments Corporation 4-27 VXI-MXI User Manual

INTX Trigger Configuration Register (on VXI-MXIs with INTX only)

VXIbus Address: Base Address + 14 (hex)

Attributes: Read/Write

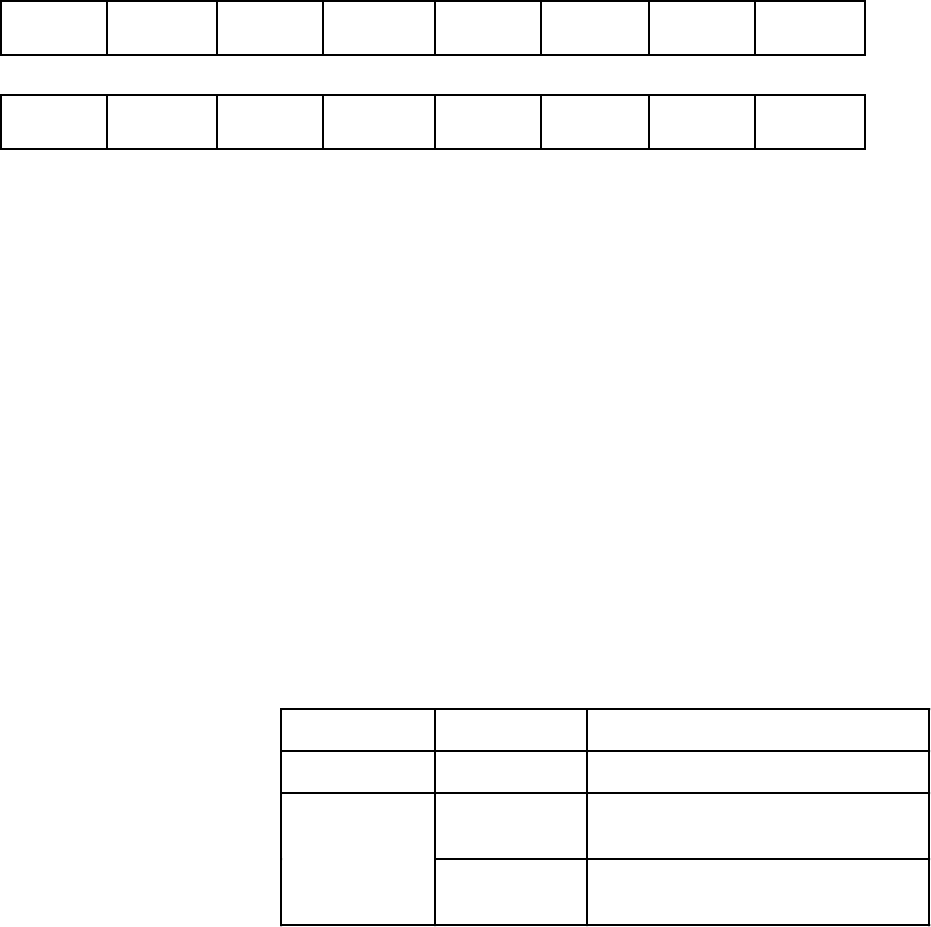

R/W

15 14 13 12 11 10 9

ETRG7EN ETRG6EN ETRG5EN ETRG4EN ETRG3EN ETRG2EN ETRG1EN ETRG0EN

8

R/W

7 65432

1

ETRG7DIR ETRG6DIR ETRG5DIR ETRG4DIR ETRG3DIR ETRG2DIR ETRG1DIR ETRG0DIR

0

This register on the INTX daughter card is used to configure the mapping of the eight VXIbus

TTL trigger lines to and from the eight INTX trigger lines.

Bit Mnemonic Description

15-8r/w ETRG[7-0]EN Extended Trigger Enable Bits

Setting these bits individually enables the corresponding VXIbus

TTL trigger lines to be mapped to the corresponding INTX trigger

lines, as specified by the corresponding ETRGxDIR bits. Clearing

these bits disables the mapping of the trigger lines to the INTX

trigger lines. These bits are cleared on a hard reset.

7-0r/w ETRG[7-0]DIR Extended Trigger Direction Bits

When the corresponding ETRGxEN bits are set, these bits control

the routing of the INTX trigger lines. When ETRGxDIR is clear,

the corresponding VXIbus TTL trigger line drives the INTX

trigger line. If the ETRGxDIR bit is set, the INTX trigger drives

the corresponding VXIbus TTL trigger line.

ETRGxEN ETRGxDIR Routing

0 X Disabled

10

VXI trigger X drives INTX

trigger line X

1 INTX trigger line X drives VXI

trigger X