Chapter 4 Register Descriptions

© National Instruments Corporation 4-33 VXI-MXI User Manual

11r MXSCTO MXIbus System Controller Timeout Status Bit

If this VXI-MXI is the MXIbus System Controller, this bit is set if

the VXI-MXI sent a MXIbus BERR on the last MXIbus transfer in

response to a MXIbus System Controller Timeout. This bit is

cleared when this register is read and on hard and soft resets.

11w ECL0EN ECL Trigger 0 Enable Bit

Setting this bit enables the ECL Trigger line 0 to be mapped to the

Trigger Out SMB connector or from the Trigger In SMB connector

on the front panel, as specified by the ECL0DIR bit. Clearing this

bit disables the mapping of ECL Trigger Line 0 to the front panel

SMB connectors. This bit is cleared on a hard reset.

10r INTLCK VXI-MXI Interlocked Bus Operation Status Bit

When this bit is set, the VXI-MXI is configured to operate in

interlocked bus mode. This mode of operation prevents deadlocks

by allowing only one master of the entire system (VXIbus and

MXIbus) at any given time. When this bit is cleared, the

VXI-MXI is configured to operate in normal mode. INTLCK is

selected with slide switch S3. This bit is not affected by hard or

soft resets.

10w ECL0DIR ECL Trigger Line 0 Direction Bit

If the ECL0EN bit is clear, this bit has no meaning. If ECL0EN is

set, this bit controls the routing of ECL trigger line 0.

If this bit is set, ECL trigger line 0 is driven by the signal received

on the front panel Trigger In SMB connector. If this bit is clear,

ECL trigger line 0 is driven out of the mainframe through the

Trigger Out SMB on the front panel. This bit is cleared on a hard

reset.

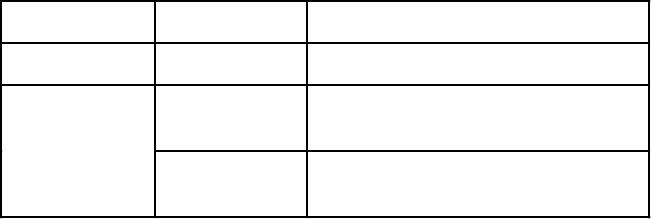

ECLxEN ECLxDIR Routing

0 X Disabled

10

ECL Trigger Line X drives TRIG

OUT SMB

1 TRIG IN SMB drives ECL

Trigger Line X

9r/w DSYSFAIL Drive SYSFAIL Bit

When this bit is set, the VXI-MXI is driving the VXIbus SYSFAIL

line active. When this bit is cleared, the VXI-MXI is not asserting

the SYSFAIL line. This bit is cleared on hard and soft reset.