© National Instruments Corporation A-1 VXI-MXI User Manual

Appendix A

Specifications

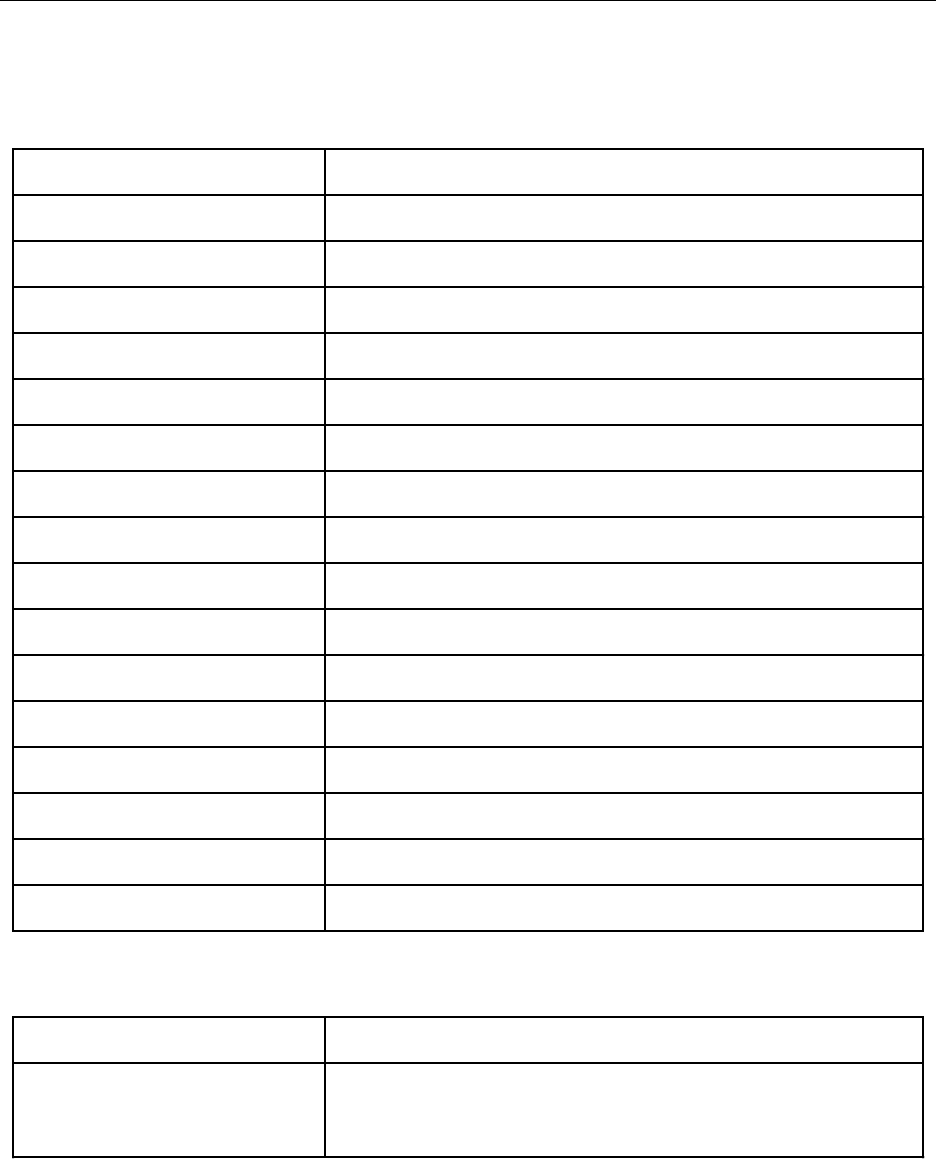

Capability Codes

VMEbus

Capability Code Description

MA32, MA24, MA16 Master Mode A32, A24, and A16 addressing

SA32, SA24, SA16 Slave Mode A32, A24, and A16 addressing

MD32, MD16, MD08(EO) Master Mode D32, D16, and D08 data sizes

SD32, SD16, SD08(EO) Slave Mode D32, D16, and D08 data sizes

MBLOCK Master Mode block transfers

SBLOCK Slave Mode block transfers

MRMW Master Mode Read/Modify/Write

SRMW Slave Mode Read/Modify/Write

PRI Prioritized arbitration

ROR Release on Request bus requester

IH Interrupt Handler

IR Interrupt Requester

ROAK Release on Acknowledge interrupter

BTO Bus Timeout

SC Optional VMEbus System Controller

IACK IACK daisy-chain driver

VXIbus

Capability Code Description

TRIG+1 Supports TTLTRIG0:7 and ECLTRIG0:1 trigger lines

and full protocol operations for each. The VXI-MXI

may participate in only one protocol operation at a time.