DC and Switching Characteristics

24 www.xilinx.com DS610-3 (v2.0) July 16, 2007

Product Specification

R

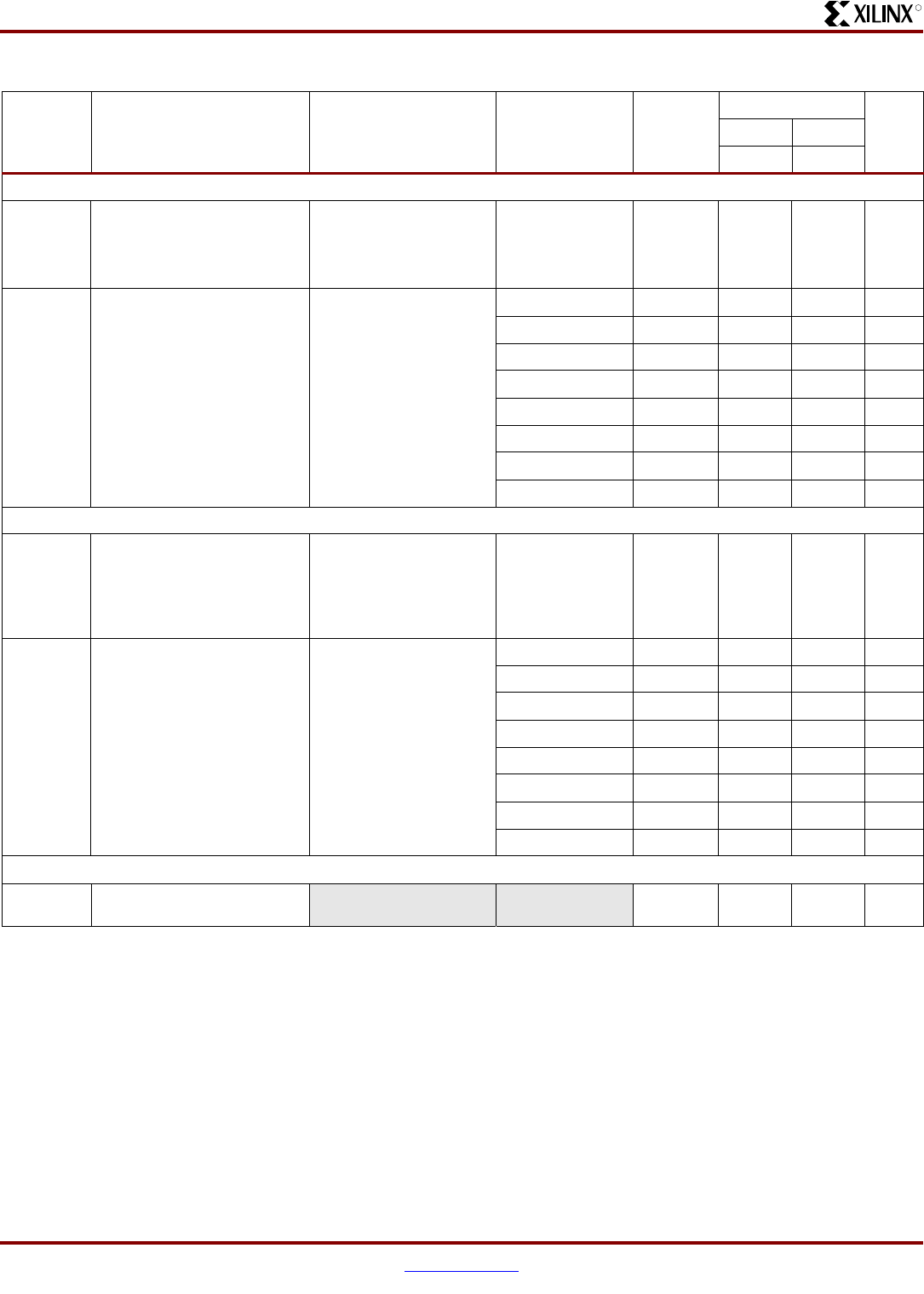

Table 19:

Setup and Hold Times for the IOB Input Path

Symbol Description Conditions

IFD_DELAY_

VALUE Device

Speed Grade

Units

-5 -4

Min Min

Setup Times

T

IOPICK

Time from the setup of data at

the Input pin to the active

transition at the ICLK input of

the Input Flip-Flop (IFF). No

Input Delay is programmed.

LVCMO S25

(2)

0 All 1.36 1.74 ns

T

IOPICKD

Time from the setup of data at

the Input pin to the active

transition at the ICLK input of

the Input Flip-Flop (IFF). The

Input Delay is programmed.

LVCMO S25

(2)

1 All 1.79 2.17 ns

2 All 2.55 2.92 ns

3 All 3.38 3.76 ns

4 All 3.75 4.32 ns

5 All 3.81 4.19 ns

6 All 4.39 5.09 ns

7 All 5.16 5.98 ns

8 All 5.69 6.57 ns

Hold Times

T

IOICKP

Time from the active transition

at the ICLK input of the Input

Flip-Flop (IFF) to the point

where data must be held at the

Input pin. No Input Delay is

programmed.

LVCMO S25

(2)

0All-0.71-0.71ns

T

IOICKPD

Time from the active transition

at the ICLK input of the Input

Flip-Flop (IFF) to the point

where data must be held at the

Input pin. The Input Delay is

programmed.

LVCMO S25

(2)

1All-1.60-1.60ns

2All-2.06-2.06ns

3All-2.46-2.46ns

4All-2.86-2.86ns

5All-2.88-2.88ns

6All-3.24-3.24ns

7All-3.55-3.55ns

8All-3.89-3.89ns

Set/Reset Pulse Width

T

RPW_IOB

Minimum pulse width to SR

control input on IOB

All 1.33 1.61 ns

Notes:

1. The numbers in this table are tested using the methodology presented in Table 25 and are based on the operating conditions set forth in

Table 7 and Table 10.

2. This setup time requires adjustment whenever a signal standard other than LVCMOS25 is assigned to the data Input. If this is true, add the

appropriate Input adjustment from Table 21.

3. These hold times require adjustment whenever a signal standard other than LVCMOS25 is assigned to the data Input. If this is true, subtract

the appropriate Input adjustment from Table 21. When the hold time is negative, it is possible to change the data before the clock’s active

edge.