DC and Switching Characteristics

DS610-3 (v2.0) July 16, 2007 www.xilinx.com 39

Product Specification

R

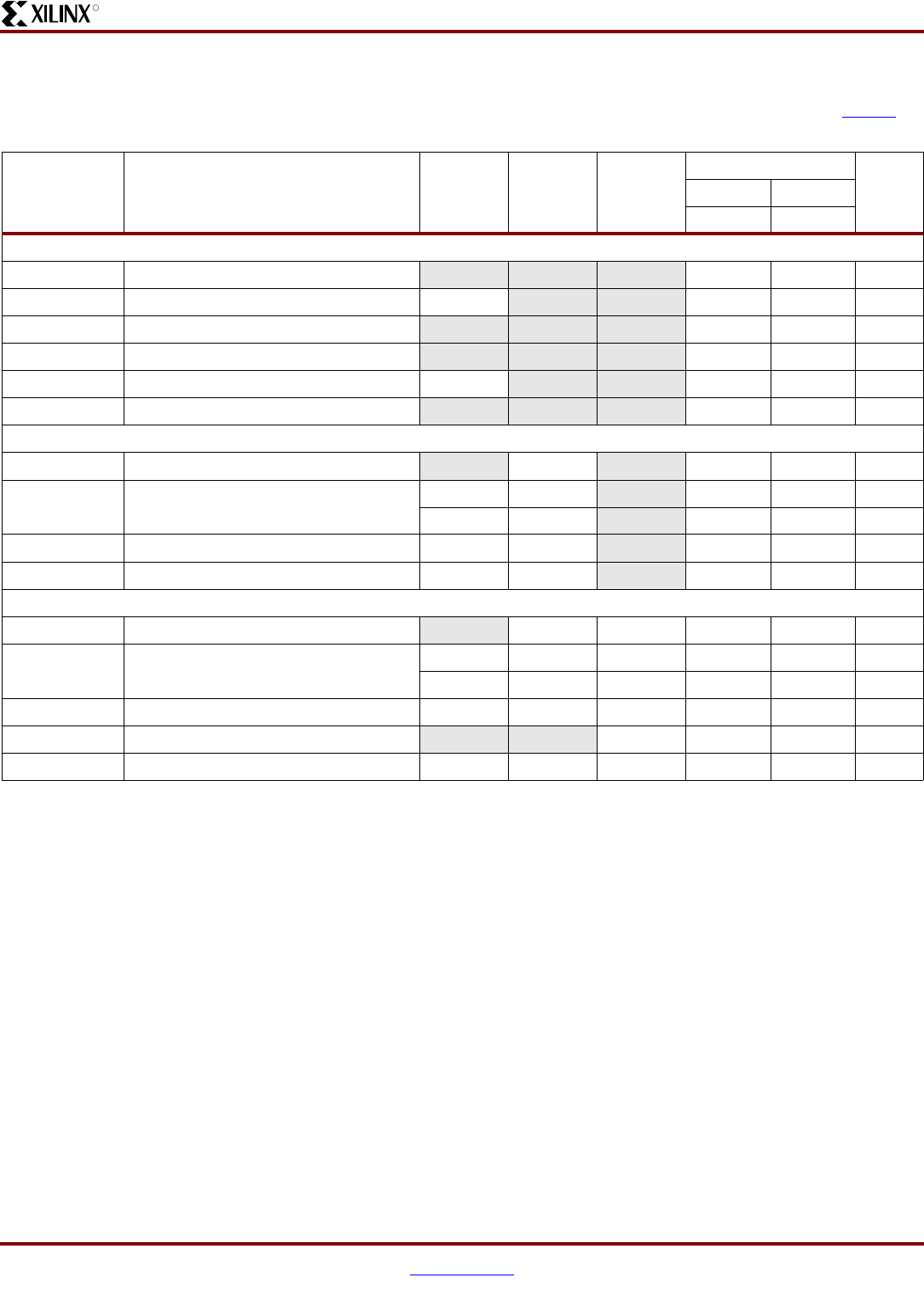

DSP48A Timing

To reference the DSP48A block diagram, see the

XtremeDSP DSP48A for Spartan-3A DSP FPGA User Guide

(UG431).

Table 33:

Setup Times for the DSP48A

Symbol Description Preadder Multiplier Postadder

Speed Grade

Units

-5 -4

Min Min

Setup Times of Data/Control Pins to the Input Register Clock

T

DSPDCK_AA

A input to A register CLK - - - 0.04 0.04 ns

T

DSPDCK_DB

D input to B register CLK Yes - - 1.64 1.88 ns

T

DSPDCK_CC

C input to C register CLK - - - 0.05 0.05 ns

T

DSPDCK_DD

D input to D register CLK - - - 0.04 0.04 ns

T

DSPDCK_OPB

OPMODE input to B register CLK Yes - - 0.37 0.42 ns

T

DSPDCK_OPOP

OPMODE input to OPMODE register CLK - - - 0.06 0.06 ns

Setup Times of Data Pins to the Pipeline Register Clock

T

DSPDCK_AM

A input to M register CLK -Yes- 3.30 3.79 ns

T

DSPDCK_BM

B input to M register CLK Yes Yes - 4.33 4.97 ns

No Yes

- 3.30 3.79 ns

T

DSPDCK_DM

D input to M register CLK Yes Yes - 4.41 5.06 ns

T

DSPDCK_OPM

OPMODE to M register CLK Yes Yes - 4.72 5.42 ns

Setup Times of Data/Control Pins to the Output Register Clock

T

DSPDCK_AP

A input to P register CLK - Yes Yes 4.78 5.49 ns

T

DSPDCK_BP

B input to P register CLK Yes Yes Yes 5.87 6.74 ns

No Yes Yes 4.77 5.48 ns

T

DSPDCK_DP

D input to P register CLK Yes Yes Yes 5.95 6.83 ns

T

DSPDCK_CP

C input to P register CLK - - Yes 1.90 2.18 ns

T

DSPDCK_OPP

OPMODE input to P register CLK Yes Yes Yes 6.25 7.18 ns