DC and Switching Characteristics

40 www.xilinx.com DS610-3 (v2.0) July 16, 2007

Product Specification

R

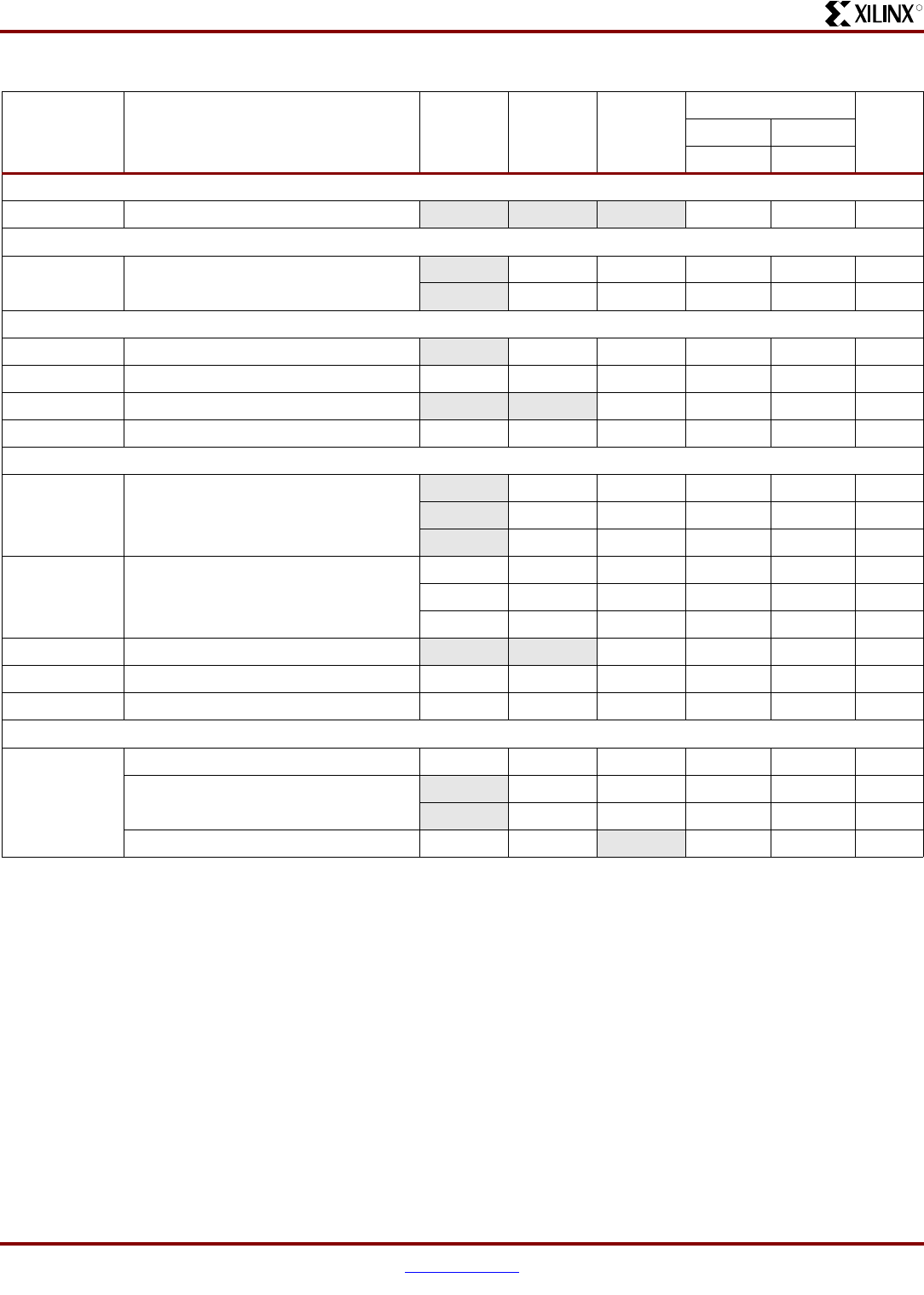

Table 34:

Clock to Out, Propagation Delays, and Maximum Frequency for the DSP48A

Symbol Description Preadder Multiplier Postadder

Speed Grade

Units

-5 -4

Max Max

Clock to Out from Output Register Clock to Output Pin

T

DSPCKO_PP

CLK (PREG) to P output - - - 1.26 1.44 ns

Clock to Out from Pipeline Register Clock to Output Pins

T

DSPCKO_PM

CLK (MREG) to P output -YesYes3.163.63ns

- Yes No 1.94 2.23 ns

Clock to Out from Input Register Clock to Output Pins

T

DSPCKO_PA

CLK (AREG) to P output -YesYes6.337.27ns

T

DSPCKO_PB

CLK (BREG) to P output Yes Yes Yes 7.45 8.56 ns

T

DSPCKO_PC

CLK (CREG) to P output - - Yes 3.37 3.87 ns

T

DSPCKO_PD

CLK (DREG) to P output Yes Yes Yes 7.33 8.42 ns

Combinatorial Delays from Input Pins to Output Pins

T

DSPDO_AP

T

DSPDO_BP

A or B input to P output - No Yes 2.78 3.19 ns

- Yes No 4.59 5.28 ns

-YesYes5.656.49ns

T

DSPDO_BP

B input to P output Yes No No 3.49 4.01 ns

Yes Yes No 5.79 6.65 ns

Ye s Ye s Ye s 6 .7 4 7 . 74 n s

T

DSPDO_CP

C input to P output - - Yes 2.76 3.17 ns

T

DSPDO_DP

D input to P output Yes Yes Yes 6.81 7.82 ns

T

DSPDO_OPP

OPMODE input to P output Yes Yes Yes 7.12 8.18 ns

Maximum Frequency

F

MAX

All registers used Yes Yes Yes 287 250 MHz

A1REG or B1REG to PREG

- Yes No 246 214 MHz

- Yes Yes 195 170 MHz

DREG, A0REG, or B0REG to MREG Yes Yes

- 205 178 MHz