DC and Switching Characteristics

DS610-3 (v2.0) July 16, 2007 www.xilinx.com 51

Product Specification

R

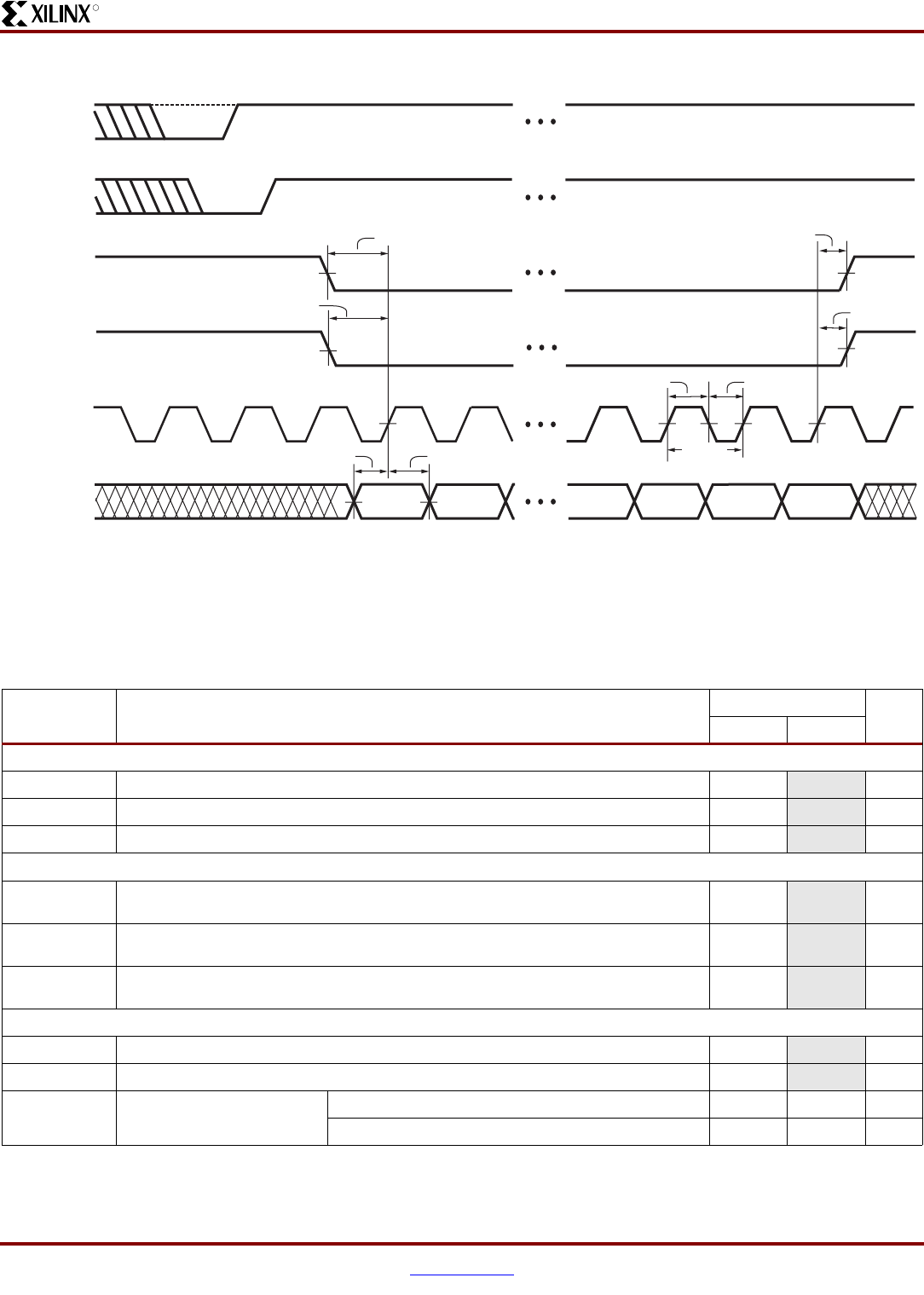

Slave Parallel Mode Timing

Figure 12:

Waveforms for Slave Parallel Configuration

Table 50:

Timing for the Slave Parallel Configuration Mode

Symbol Description

All Speed Grades

UnitsMin Max

Setup Times

T

SMDCC

(2)

The time from the setup of data at the D0-D7 pins to the rising transition at the CCLK pin 7 -ns

T

SMCSCC

Setup time on the CSI_B pin before the rising transition at the CCLK pin 7 -ns

T

SMCCW

Setup time on the RDWR_B pin before the rising transition at the CCLK pin 17 -ns

Hold Times

T

SMCCD

The time from the rising transition at the CCLK pin to the point when data is last held at

the D0-D7 pins

1 -ns

T

SMCCCS

The time from the rising transition at the CCLK pin to the point when a logic level is last

held at the CSO_B pin

0 -ns

T

SMWCC

The time from the rising transition at the CCLK pin to the point when a logic level is last

held at the RDWR_B pin

0 -ns

Clock Timing

T

CCH

The High pulse width at the CCLK input pin 5 -ns

T

CCL

The Low pulse width at the CCLK input pin 5 -ns

F

CCPAR

Frequency of the clock signal

at the CCLK input pin

No bitstream compression 0 80 MHz

With bitstream compression 0 80 MHz

Notes:

1. The numbers in this table are based on the operating conditions set forth in Table 7.

2. Some Xilinx documents refer to Parallel modes as “SelectMAP” modes.

DS529-3_02_051607

Byte 0 Byte 1 Byte n Byte n+1

T

SMWCC

1/F

CCPAR

T

SMCCCS

T

SCCH

T

SMCCW

T

SMCCD

T

SMCSCC

T

SMDCC

PROG_B

(Input)

(Open-Drain)

INIT_B

(Input)

CSI_B

RDWR_B

(Input)

(Input)

CCLK

(Inputs)

D0 - D7

T

MCCH

T

SCCL

T

MCCL

Notes:

1. It is possible to abort configuration by pulling CSI_B Low in a given CCLK cycle, then switching RDWR_B Low or High in any subsequent

cycle for which CSI_B remains Low. The RDWR_B pin asynchronously controls the driver impedance of the D0 - D7 bus. When RDWR_B

switches High, be careful to avoid contention on the D0 - D7 bus.