Pinout Descriptions

96 www.xilinx.com DS610-4 (v2.0) July 16, 2007

Product Specification

R

Migration Recommendations

There are multiple pinout differences between the

XC3SD1800A and the XC3SD3400A FPGAs in the FG676

package. Please note the differences between the two

devices from Ta bl e 67 and take the necessary precautions.

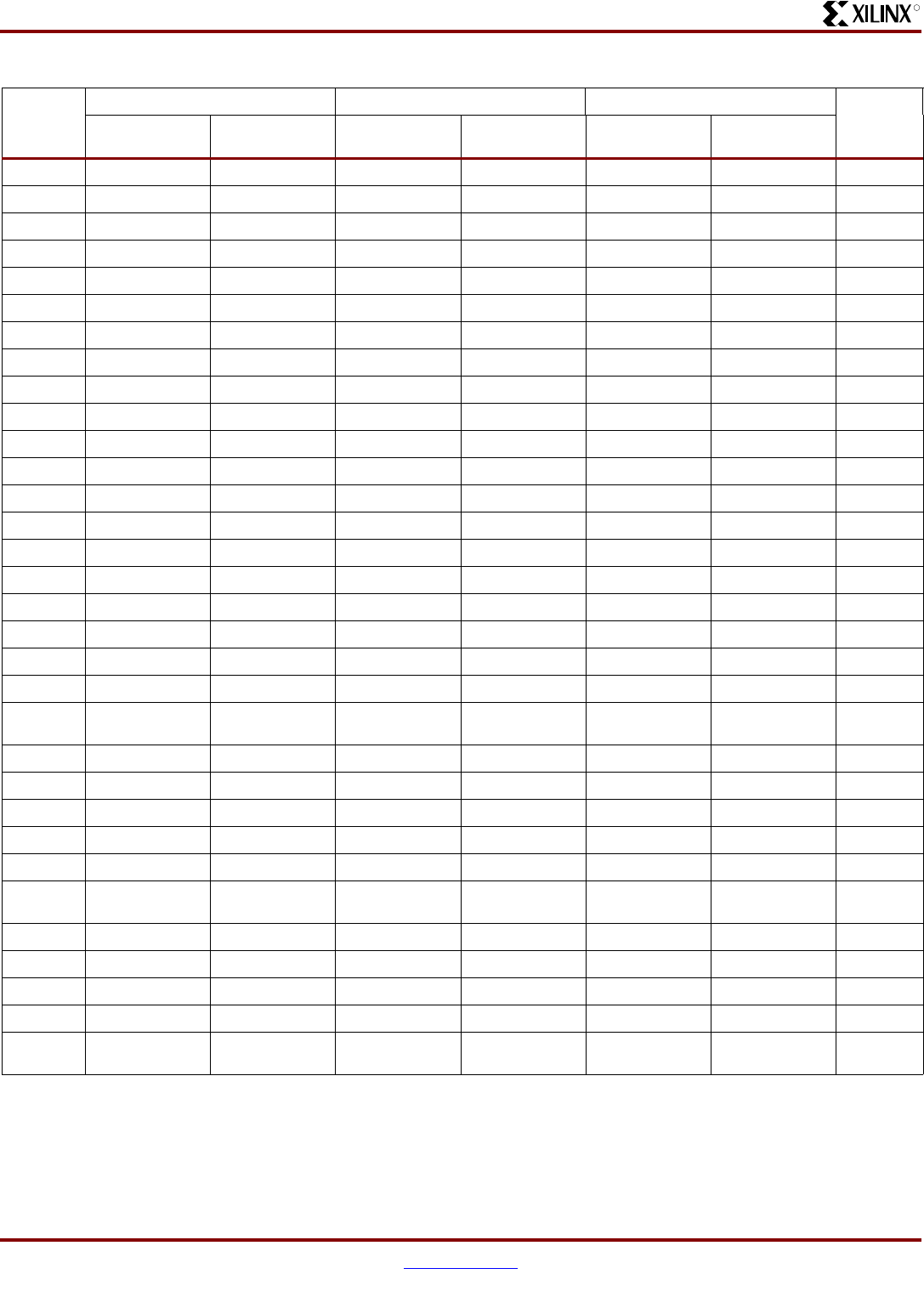

Y8 N.C. N.C. IP_2 2 VCCINT VCCINT Y8

Y11 IP_2 2 IP_2 2 VCCINT VCCINT Y11

Y18 N.C. N.C. IP_2 2 VCCINT VCCINT Y18

Y19 N.C. N.C. IP_2/VREF_2 2 VCCINT VCCINT Y19

W18 N.C. N.C. IP_2 2 VCCINT VCCINT W18

AF2 IP_2 2 IP_2 2 VCCAUX VCCAUX AF2

AF7 IP_2 2 IP_2 2 VCCO_2 2 AF7

AD5 N.C. N.C. IP_2 2 GND GND AD5

AD23 N.C. N.C. IP_2 2 GND GND AD23

AC5 N.C. N.C. IP_2 2 GND GND AC5

AC7 IP_2 2 IP_2 2 GND GND AC7

AC18 IP_2 2 IP_2 2 GND GND AC18

AB10 IP_2/VREF_2 2 IP_2/VREF_2 2 GND GND AB10

AB17 IP_2 2 IP_2 2 VCCAUX VCCAUX AB17

AB20 IP_2 2 IP_2 2 GND GND AB20

AA8 N.C. N.C. IP_2 2 VCCINT VCCINT AA8

AA19 IP_2 2 IP_2 2 GND GND AA19

AC22 N.C. N.C. IO_2 2 IO_2 2 AC22

Y3 IP_L54P_3 3 IP_L54P_3 3 IP_3 3 Y3

Y4 IP_L54N_3 3 IP_L54N_3 3 VCCINT VCCINT Y4

H4 IP_L12N_3/

VREF_3

3 IP_L12N_3/

VREF_3

3 IP_3/VREF_3 3 H4

G1 IP_L16N_3 3 IP_L16N_3 3 IP_3 3 G1

G2 IP_L16P_3 3 IP_L16P_3 3 GND GND G2

G5 IP_L12P_3 3 IP_L12P_3 3 GND GND G5

D1 IP_L08N_3 3 IP_L08N_3 3 VCCAUX VCCAUX D1

D2 IP_L08P_3 3 IP_L08P_3 3 GND GND D2

C1 IP_L04N_3/

VREF_3

3 IP_L04N_3/

VREF_3

3 IP_3/VREF_3 3 C1

C2 IP_L04P_3 3 IP_L04P_3 3 VCCO_3 3 C2

AB3 IP_L62P_3 3 IP_L62P_3 3 GND GND AB3

AB4 IP_L62N_3 3 IP_L62N_3 3 VCCAUX VCCAUX AB4

AA4 IP_L58P_3 3 IP_L58P_3 3 GND GND AA4

AA5 IP_L58N_3/

VREF_3

3 IP_L58N_3/

VREF_3

3 IP_3/VREF_3 3 AA5

Table 67:

FG676 Footprint Migration Differences

(Continued)

Spartan-3A Spartan-3A DSP Spartan-3A DSP

FG676

Ball

XC3S1400A

Type

XC3S1400A

Bank

XC3SD1800A

Type

XC3SD1800A

Bank

XC3SD3400A

Type

XC3SD3400A

Bank

FG676

Ball