DC and Switching Characteristics

46 www.xilinx.com DS610-3 (v2.0) July 16, 2007

Product Specification

R

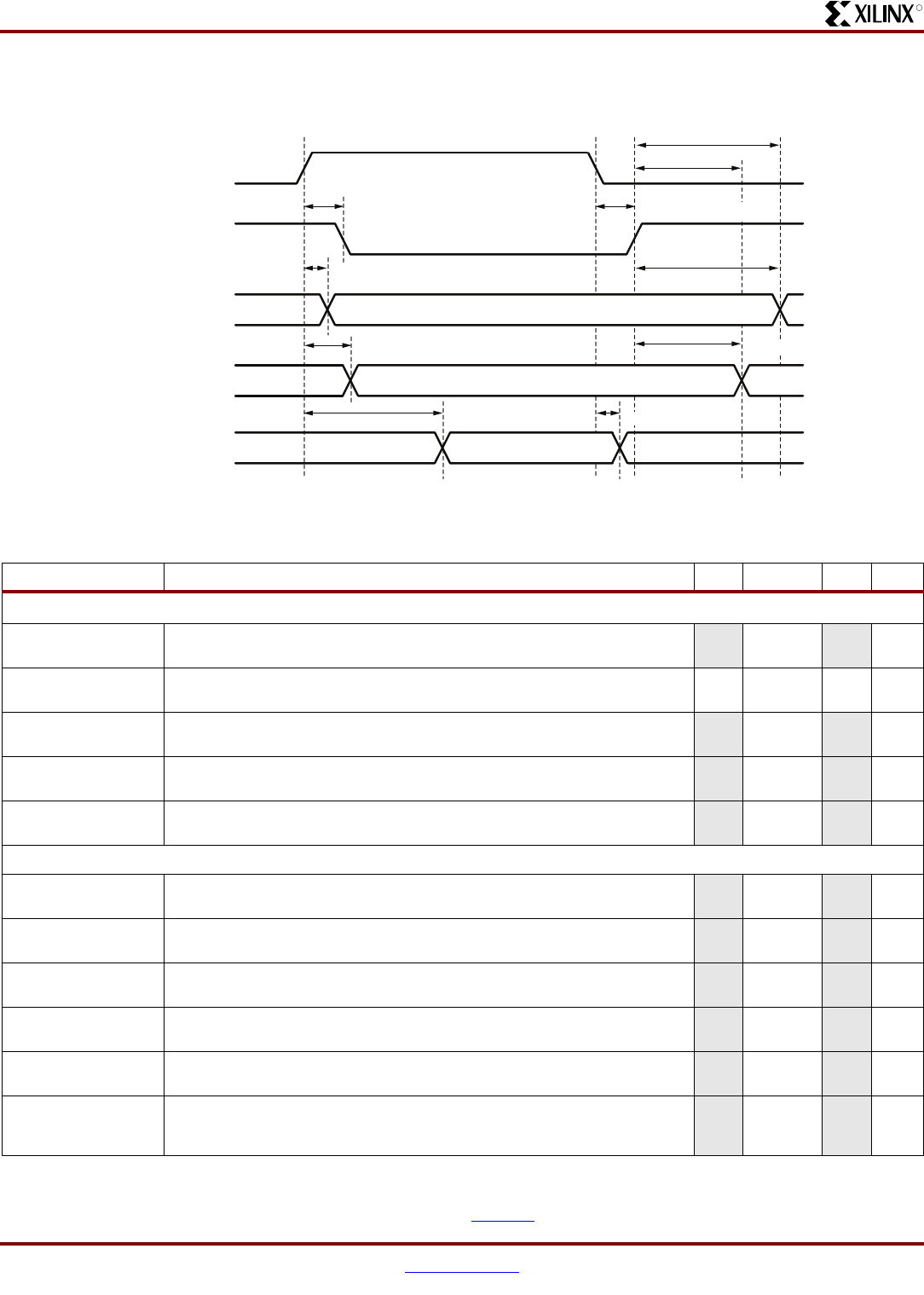

Suspend Mode Timing

Figure 9:

Suspend Mode Timing

DS610-3_08_061207

Blocked

t

SUSPEND_DISABLE

t

SUSPEND_GWE

t

SUSPENDHIGH_AWAKE

t

AWAKE_GWE

t

AWAKE_GTS

t

SUSPEND_GTS

SUSPEND Input

AWAKE Output

Flip-Flops, Block RAM,

Distributed RAM

FPGA Outputs

FPGA Inputs,

Interconnect

Write Protected

Defined by SUSPEND constraint

Entering Suspend Mode Exiting Suspend Mode

sw_gts_cycle

sw_gwe_cycle

t

SUSPEND_ENABLE

t

SUSPENDLOW_AWAKE

Table 43:

Suspend Mode Timing Parameters

Symbol Description Min Typ Max Units

Entering Suspend Mode

T

SUSPENDHIGH_AWAKE

Rising edge of SUSPEND pin to falling edge of AWAKE pin without glitch filter

(

suspend_filter:No

)

–7–ns

T

SUSPENDFILTER

Adjustment to SUSPEND pin rising edge parameters when glitch filter

enabled (

suspend_filter:Yes

)

+160 +300 +600 ns

T

SUSPEND_GWE

Rising edge of SUSPEND pin until FPGA output pins drive their defined

SUSPEND constraint behavior

–10–ns

T

SUSPEND_GTS

Rising edge of SUSPEND pin to write-protect lock on all writable clocked

elements

–<5–ns

T

SUSPEND_DISABLE

Rising edge of the SUSPEND pin to FPGA input pins and interconnect

disabled

–340–ns

Exiting Suspend Mode

T

SUSPENDLOW_AWAKE

Falling edge of the SUSPEND pin to rising edge of the AWAKE pin. Does not

include DCM lock time.

– 4 to 108 – μs

T

SUSPEND_ENABLE

Falling edge of the SUSPEND pin to FPGA input pins and interconnect

re-enabled

– 3.7 to 109 – μs

T

AWAKE_GWE1

Rising edge of the AWAKE pin until write-protect lock released on all writable

clocked elements, using

sw_clk:InternalClock

and

sw_gwe_cycle:1

.

–67–ns

T

AWAKE_GWE512

Rising edge of the AWAKE pin until write-protect lock released on all writable

clocked elements, using

sw_clk:InternalClock

and

sw_gwe_cycle:512

.

–14– μs

T

AWAKE_GTS1

Rising edge of the AWAKE pin until outputs return to the behavior described

in the FPGA application, using

sw_clk:InternalClock

and

sw_gts_cycle:1

.

–57–ns

T

AWAKE_GTS512

Rising edge of the AWAKE pin until outputs return to the behavior described

in the FPGA application, using

sw_clk:InternalClock

and

sw_gts_cycle:512

.

–14– μs

Notes:

1. These parameters based on characterization.

2. For information on using the Spartan-3A DSP Suspend feature, see XAPP480

:

Using Suspend Mode in Spartan-3 Generation FPGAs

.