DC and Switching Characteristics

DS610-3 (v2.0) July 16, 2007 www.xilinx.com 31

Product Specification

R

Timing Measurement Methodology

When measuring timing parameters at the programmable

I/Os, different signal standards call for different test

conditions. Table 25 lists the conditions to use for each

standard.

The method for measuring Input timing is as follows: A

signal that swings between a Low logic level of V

L

and a

High logic level of V

H

is applied to the Input under test.

Some standards also require the application of a bias

voltage to the V

REF

pins of a given bank to properly set the

input-switching threshold. The measurement point of the

Input signal (V

M

) is commonly located halfway between V

L

and V

H

.

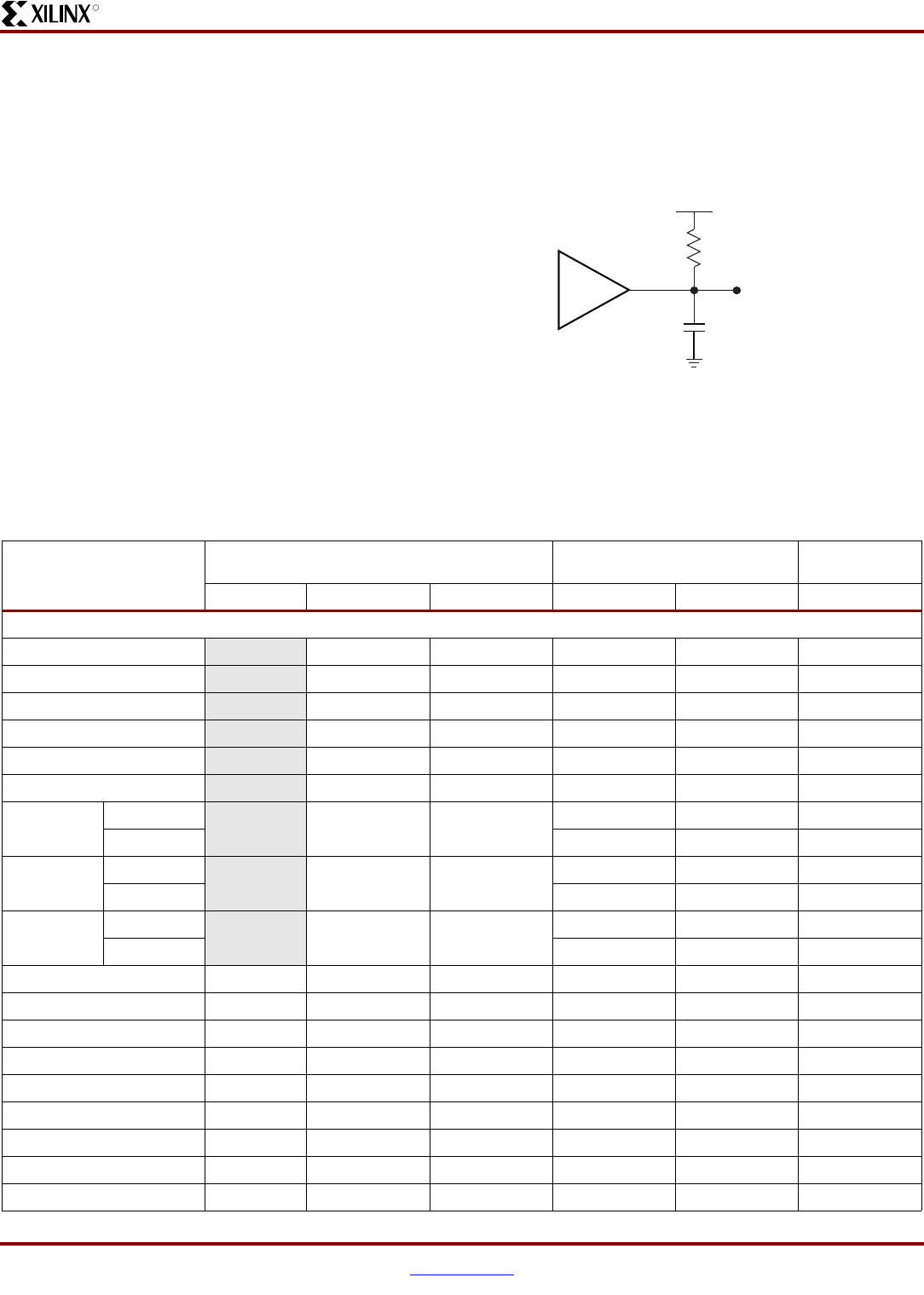

The Output test setup is shown in Figure 8. A termination

voltage V

T

is applied to the termination resistor R

T

, the other

end of which is connected to the Output. For each standard,

R

T

and V

T

generally take on the standard values

recommended for minimizing signal reflections. If the

standard does not ordinarily use terminations (for example,

LVCMOS, LVTTL), then R

T

is set to 1MΩ to indicate an

open connection, and V

T

is set to zero. The same

measurement point (V

M

) that was used at the Input is also

used at the Output.

Figure 8:

Output Test Setup

FPGA Output

V

T

(V

REF

)

R

T

(R

REF

)

V

M

(V

MEAS

)

C

L

(C

REF

)

DS312-3_04_102406

Notes:

1. The names shown in parentheses are

used in the IBIS file.

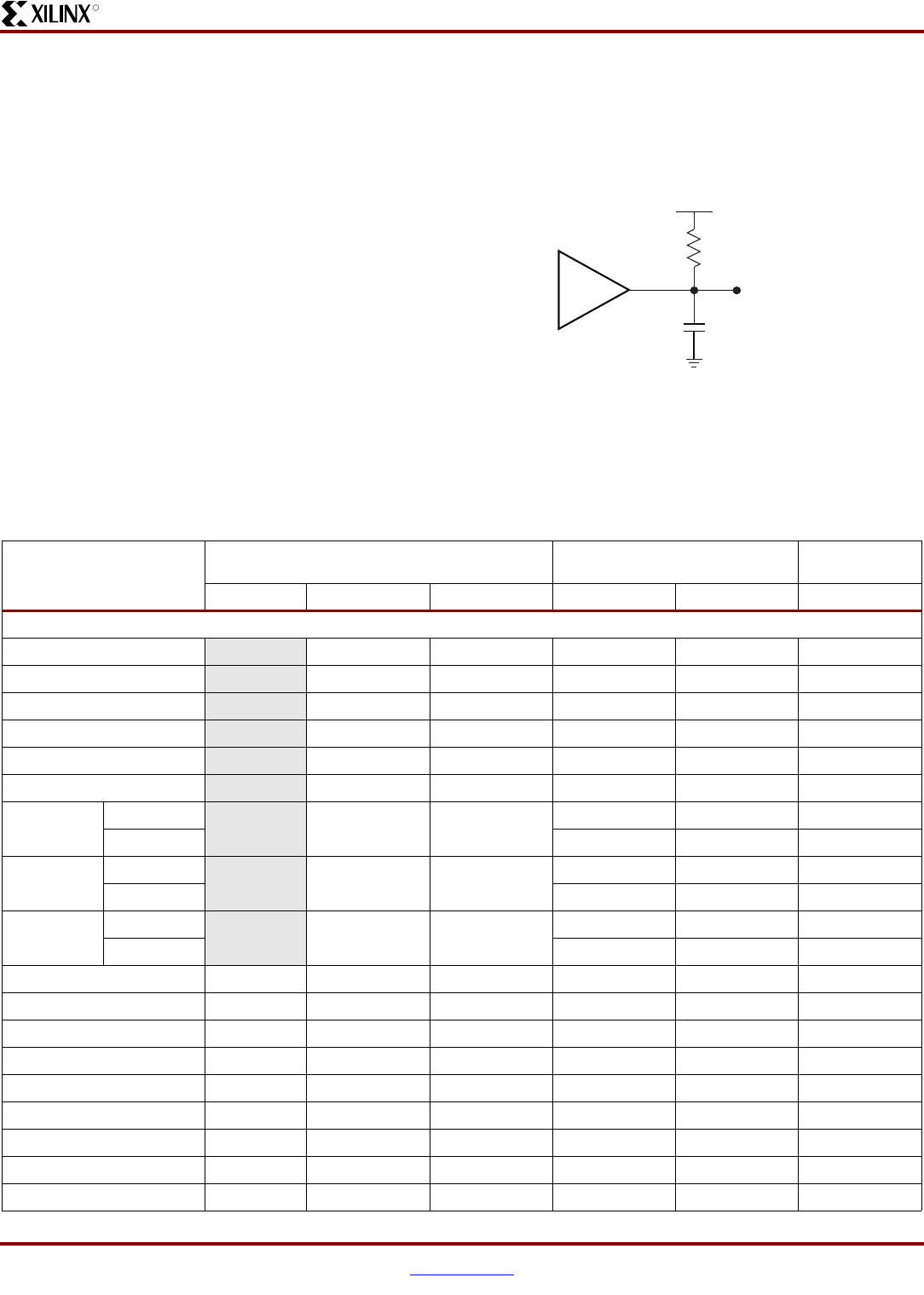

Table 25:

Test Methods for Timing Measurement at I/Os

Signal Standard

(IOSTANDARD)

Inputs Outputs

Inputs and

Outputs

V

REF

(V) V

L

(V) V

H

(V) R

T

(Ω) V

T

(V) V

M

(V)

Single-Ended

LVTTL - 0 3.3 1M 0 1.4

LVCMOS33 - 0 3.3 1M 0 1.65

LVCMOS25 - 0 2.5 1M 0 1.25

LVCMOS18 - 0 1.8 1M 0 0.9

LVCMOS15 - 0 1.5 1M 0 0.75

LVCMOS12 - 0 1.2 1M 0 0.6

PCI33_3 Rising - Note 3 Note 3 25 0 0.94

Falling 25 3.3 2.03

PCI66_3 Rising - Note 3 Note 3 25 0 0.94

Falling 25 3.3 2.03

PCIX Rising - Note 3 Note 3 25 0 0.94

Falling 25 3.3 2.03

HSTL_I 0.75 V

REF

– 0.5 V

REF

+ 0.5 50 0.75 V

REF

HSTL_III 0.9 V

REF

– 0.5 V

REF

+ 0.5 50 1.5 V

REF

HSTL_I_18 0.9 V

REF

– 0.5 V

REF

+ 0.5 50 0.9 V

REF

HSTL_II_18 0.9 V

REF

– 0.5 V

REF

+ 0.5 25 0.9 V

REF

HSTL_III_18 1.1 V

REF

– 0.5 V

REF

+ 0.5 50 1.8 V

REF

SSTL18_I 0.9 V

REF

– 0.5 V

REF

+ 0.5 50 0.9 V

REF

SSTL18_II 0.9 V

REF

– 0.5 V

REF

+ 0.5 25 0.9 V

REF

SSTL2_I 1.25 V

REF

– 0.75 V

REF

+ 0.75 50 1.25 V

REF

SSTL2_II 1.25 V

REF

– 0.75 V

REF

+ 0.75 25 1.25 V

REF