DC and Switching Characteristics

DS610-3 (v2.0) July 16, 2007 www.xilinx.com 49

Product Specification

R

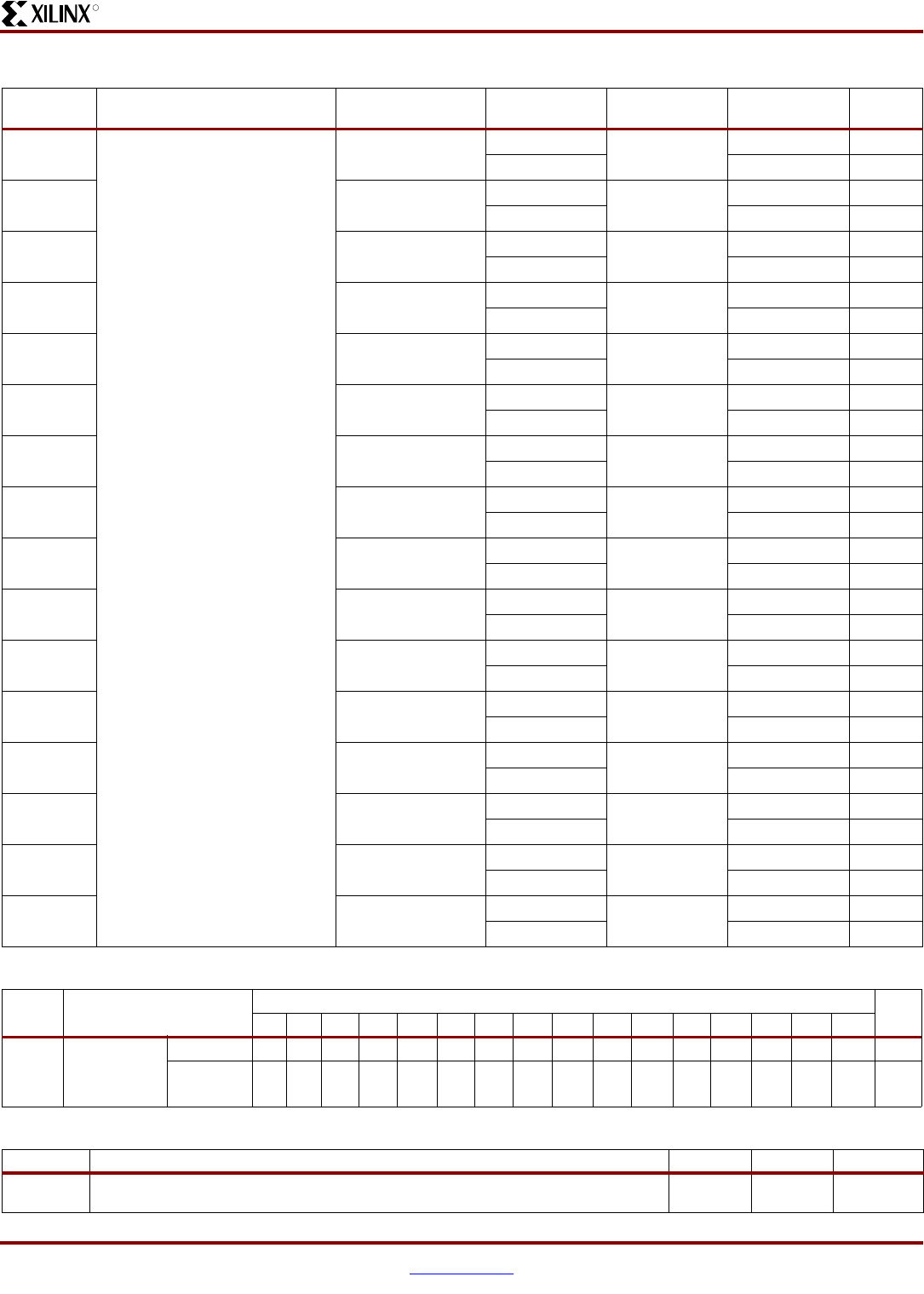

Table 46:

Master Mode CCLK Output Frequency by

ConfigRate

Option Setting

Symbol Description

ConfigRate

Setting

Temperature

Range Minimum Maximum Units

F

CCLK1

Equivalent CCLK clock frequency

by

ConfigRate

setting

1

(power-on value)

Commercial

0.400

0.797 MHz

Industrial 0.847 MHz

F

CCLK3

3

Commercial

1.20

2.42 MHz

Industrial 2.57 MHz

F

CCLK6

6

Commercial

2.40

4.83 MHz

Industrial 5.13 MHz

F

CCLK7

7

Commercial

2.80

5.61 MHz

Industrial 5.96 MHz

F

CCLK8

8

Commercial

3.20

6.41 MHz

Industrial 6.81 MHz

F

CCLK10

10

Commercial

4.00

8.12 MHz

Industrial 8.63 MHz

F

CCLK12

12

Commercial

4.80

9.70 MHz

Industrial 10.31 MHz

F

CCLK13

13

Commercial

5.20

10.69 MHz

Industrial 11.37 MHz

F

CCLK17

17

Commercial

6.80

13.74 MHz

Industrial 14.61 MHz

F

CCLK22

22

Commercial

8.80

18.44 MHz

Industrial 19.61 MHz

F

CCLK25

25

Commercial

10.00

20.90 MHz

Industrial 22.23 MHz

F

CCLK27

27

Commercial

10.80

22.39 MHz

Industrial 23.81 MHz

F

CCLK33

33

Commercial

13.20

27.48 MHz

Industrial 29.23 MHz

F

CCLK44

44

Commercial

17.60

37.60 MHz

Industrial 40.00 MHz

F

CCLK50

50

Commercial

20.00

44.80 MHz

Industrial 47.66 MHz

F

CCLK100

100

Commercial

40.00

88.68 MHz

Industrial 94.34 MHz

Table 47:

Master Mode CCLK Output Minimum Low and High Time

Symbol Description

ConfigRate

Setting

Units13 6 7 810121317222527334450100

T

MCCL,

T

MCCH

Master Mode

CCLK

Minimum Low

and High Time

Commercial

595 196 98.3 84.5 74.1 58.4 48.9 44.1 34.2 25.6 22.3 20.9 17.1 12.3 10.4 5.3

ns

Industrial

560 185 92.6 79.8 69.8 55.0 46.0 41.8 32.3 24.2 21.4 20.0 16.2 11.9 10.0 5.0

ns

Table 48:

Slave Mode CCLK Input Low and High Time

Symbol Description Min Max Units

T

SCCL,

T

SCCH

CCLK Low and High time 5

∞

ns