Chapter 5 Cache and Memory Optimizations 97

Software Optimization Guide for AMD64 Processors

25112 Rev. 3.06 September 2005

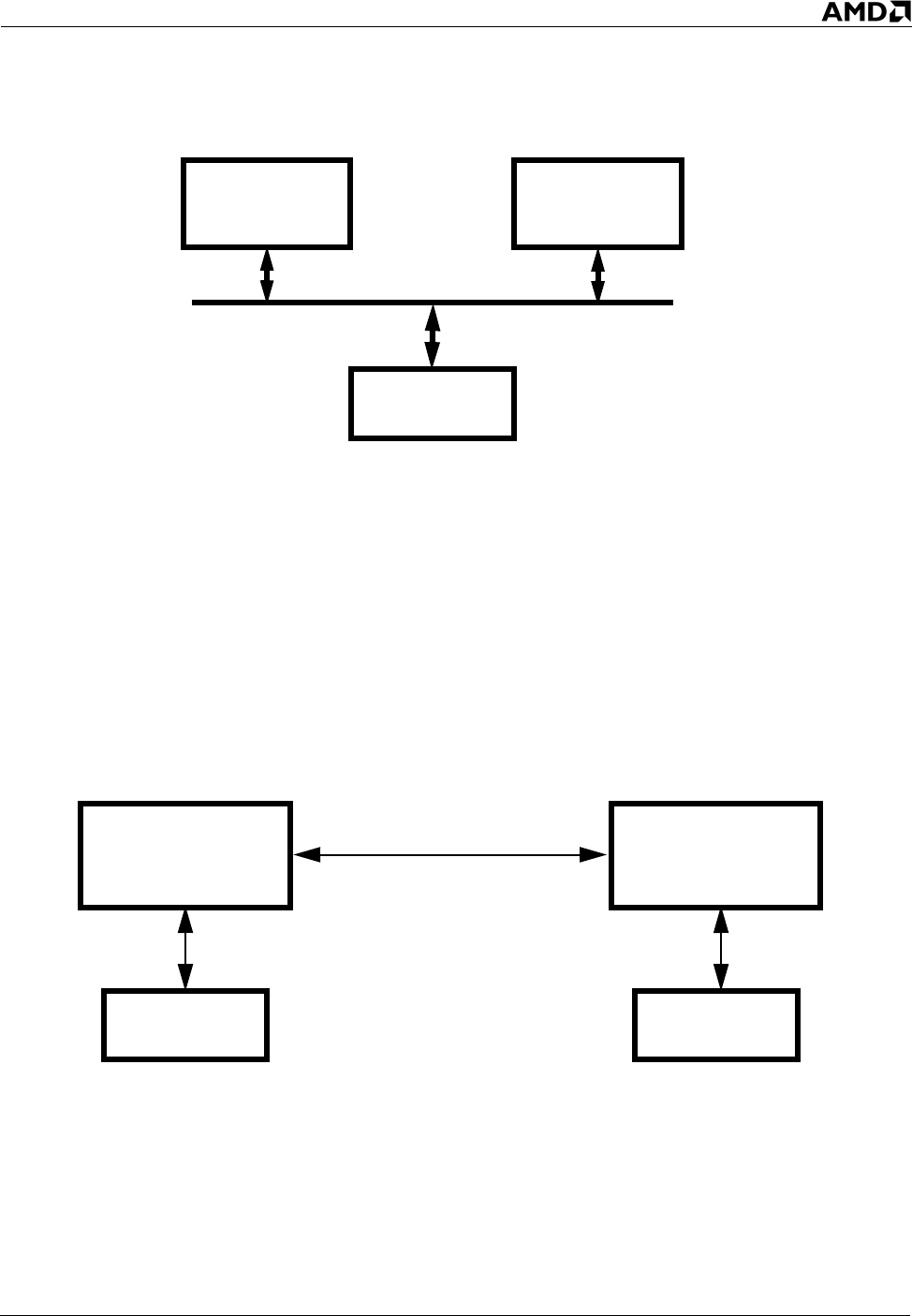

Figure 1. Simple SMP Block Diagram

The AMD Opteron processor implements a Cache-coherent nonuniform memory access (ccNUMA)

architecture when two or more processors are connected together on the same motherboard. In a

ccNUMA design, each processor has its own memory system. When a processor accesses memory on

its own local memory system, the latency is relatively low, especially when compared to a similar

SMP system. If a processor accesses memory located on a different processor, then the latency will be

higher. The phrase ‘non-uniform memory access’ refers to this potential difference in latency.

In an AMD Opteron processor system, each processor contains its own memory controller. Figure 2

shows an example of a two processor AMD Opteron system in a ccNUMA configuration.

Figure 2. AMD Opteron

Dual-Core AMD Opteron processors and AMD Athlon X2 Dual-Core processors share the on-chip

integrated memory controller and memory. Two or more AMD dual-core processors still use the

ccNUMA configuration. Figure 3 illustrates a dual-core AMD Opteron configuration.

CPU0 CPU1

Memory

AMD Opteron™

Memory

CPU0

AMD Opteron™

CPU1

HyperTransport™

Memory