Appendix C Instruction Latencies 327

Software Optimization Guide for AMD64 Processors

25112 Rev. 3.06 September 2005

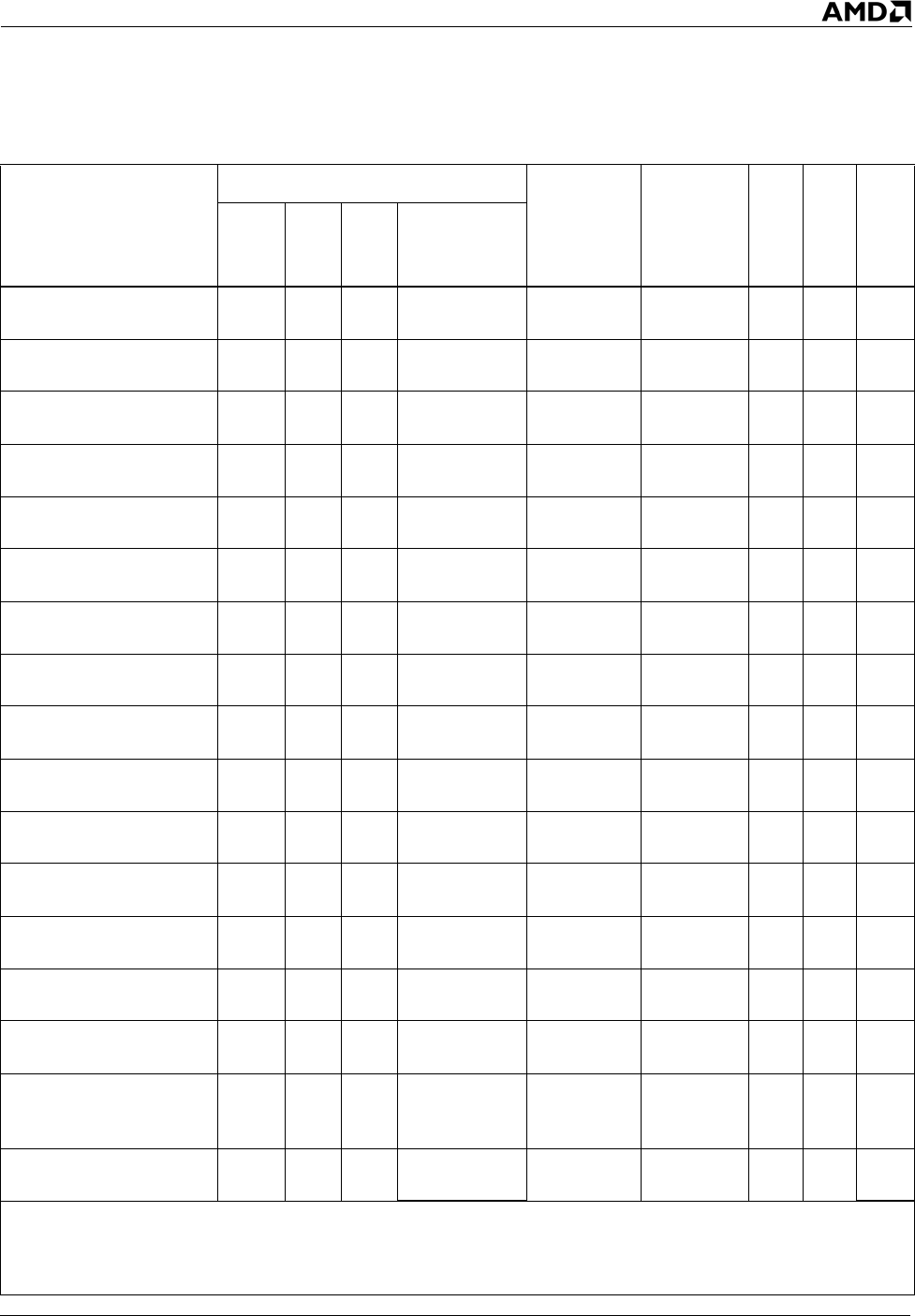

CVTDQ2PS xmmreg1,

xmmreg2

0Fh 5Bh 11-xxx-xxx Double FSTORE 5 1/2

CVTDQ2PS xmmreg,

mem128

0Fh 5Bh mm-xxx-xxx Double FSTORE 7 1/2

CVTPD2DQ xmmreg1,

xmmreg2

F2h 0Fh E6h 11-xxx-xxx VectorPath ~ 8

CVTPD2DQ xmmreg,

mem128

F2h 0Fh E6h mm-xxx-xxx VectorPath ~ 10

CVTPD2PI mmreg,

xmmreg

66h 0Fh 2Dh 11-xxx-xxx VectorPath ~ 8 1/2

CVTPD2PI mmreg,

mem128

66h 0Fh 2Dh mm-xxx-xxx VectorPath ~ 10 1/2

CVTPD2PS xmmreg1,

xmmreg2

66h 0Fh 5Ah 11-xxx-xxx VectorPath ~ 8

CVTPD2PS xmmreg,

mem128

66h 0Fh 5Ah mm-xxx-xxx VectorPath ~ 10

CVTPI2PD xmmreg,

mmreg

66H 0FH 2Ah 11-xxx-xxx Double FSTORE 5 1/2

CVTPI2PD xmmreg,

mem64

66H 0FH 2Ah mm-xxx-xxx Double FSTORE 7 1/2

CVTPS2DQ xmmreg1,

xmmreg2

66h 0Fh 5Bh 11-xxx-xxx Double FSTORE 5 1/2

CVTPS2DQ xmmreg,

mem128

66h 0Fh 5Bh mm-xxx-xxx Double FSTORE 7 1/2

CVTPS2PD xmmreg1,

xmmreg2

0Fh 5Ah 11-xxx-xxx Double ~ 3 1/2

CVTPS2PD xmmreg,

mem64

0Fh 5Ah mm-xxx-xxx Double ~ 5 1/2

CVTSD2SI reg32/64,

xmmreg

F2h 0Fh 2Dh 11-xxx-xxx Double FSTORE 9 1/1

CVTSD2SI reg32/64,

mem64

F2h 0Fh 2Dh mm-xxx-xxx VectorPath FADD/

FMUL/

FSTORE

10 1/1

CVTSD2SS xmmreg1,

xmmreg2

F2h 0Fh 5Ah 11-xxx-xxx VectorPath FSTORE 12

Table 19. SSE2 Instructions (Continued)

Syntax

Encoding

Decode

type

FPU

pipe(s)

Latency

Throughput

Note

Prefix

byte

First

byte

2nd

byte

ModRM byte

Notes:

1. The low half of the result is available one cycle earlier than listed.

2. This is the execution latency for the instruction. The time to complete the external write depends on the memory

speed and the hardware implementation.