316 Instruction Latencies Appendix C

25112 Rev. 3.06 September 2005

Software Optimization Guide for AMD64 Processors

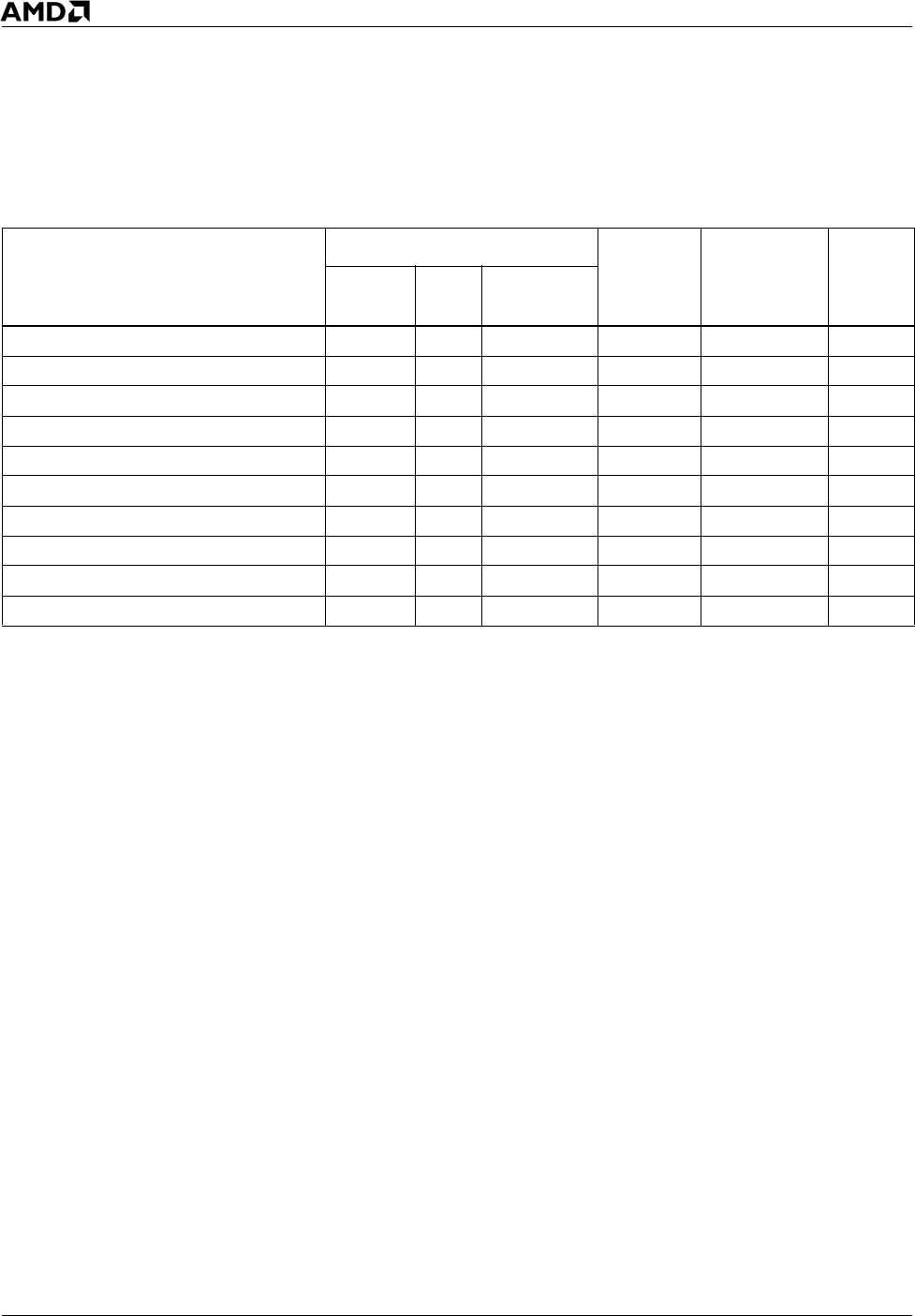

C.6 3DNow!™ Technology Extensions

Table 17. 3DNow!™ Technology Extensions

Syntax

Encoding

Decode

type

FPU

pipe(s)

Latency

Prefix

byte(s)

imm8

ModRM

byte

PF2IW mmreg1, mmreg2 0Fh, 0Fh 1Ch 11-xxx-xxx DirectPath FADD 4

PF2IW mmreg, mem64 0Fh, 0Fh 1Ch mm-xxx-xxx DirectPath FADD 6

PFNACC mmreg1, mmreg2 0Fh, 0Fh 8Ah 11-xxx-xxx DirectPath FADD 4

PFNACC mmreg, mem64 0Fh, 0Fh 8Ah mm-xxx-xxx DirectPath FADD 6

PFPNACC mmreg1, mmreg2 0Fh, 0Fh 8Eh 11-xxx-xxx DirectPath FADD 4

PFPNACC mmreg, mem64 0Fh, 0Fh 8Eh mm-xxx-xxx DirectPath FADD 6

PI2FW mmreg1, mmreg2 0Fh, 0Fh 0Ch 11-xxx-xxx DirectPath FADD 4

PI2FW mmreg, mem64 0Fh, 0Fh 0Ch mm-xxx-xxx DirectPath FADD 6

PSWAPD mmreg1, mmreg2 0Fh, 0Fh BBh 11-xxx-xxx DirectPath FADD/FMUL 2

PSWAPD mmreg, mem64 0Fh, 0Fh BBh mm-xxx-xxx DirectPath FADD/FMUL 4