314 Instruction Latencies Appendix C

25112 Rev. 3.06 September 2005

Software Optimization Guide for AMD64 Processors

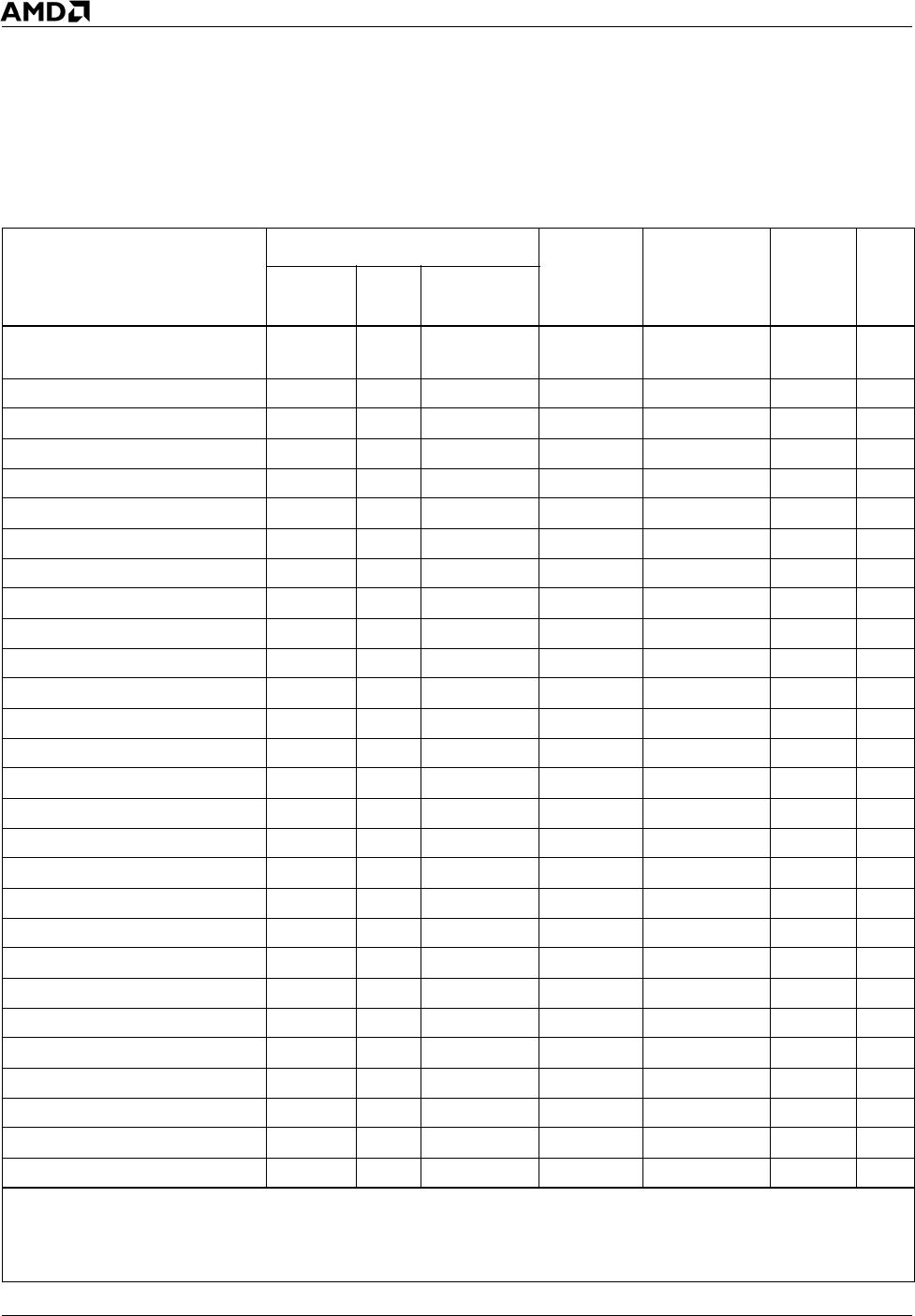

C.5 3DNow!™ Technology Instructions

Table 16. 3DNow!™ Technology Instructions

Syntax

Encoding

Decode

type

FPU

pipe(s)

Latency Note

Prefix

byte(s)

imm8

ModRM

byte

FEMMS 0Fh 0Eh DirectPath FADD/FMUL/

FSTORE

22

PAVGUSB mmreg1, mmreg2 0Fh, 0Fh BFh 11-xxx-xxx DirectPath FADD/FMUL 2

PAVGUSB mmreg, mem64 0Fh, 0Fh BFh mm-xxx-xxx DirectPath FADD/FMUL 4

PF2ID mmreg1, mmreg2 0Fh, 0Fh 1Dh 11-xxx-xxx DirectPath FADD 4

PF2ID mmreg, mem64 0Fh, 0Fh 1Dh mm-xxx-xxx DirectPath FADD 6

PFACC mmreg1, mmreg2 0Fh, 0Fh AEh 11-xxx-xxx DirectPath FADD 4

PFACC mmreg, mem64 0Fh, 0Fh AEh mm-xxx-xxx DirectPath FADD 6

PFADD mmreg1, mmreg2 0Fh, 0Fh 9Eh 11-xxx-xxx DirectPath FADD 4

PFADD mmreg, mem64 0Fh, 0Fh 9Eh mm-xxx-xxx DirectPath FADD 6

PFCMPEQ mmreg1, mmreg2 0Fh, 0Fh B0h 11-xxx-xxx DirectPath FADD 2

PFCMPEQ mmreg, mem64 0Fh, 0Fh B0h mm-xxx-xxx DirectPath FADD 4

PFCMPGE mmreg1, mmreg2 0Fh, 0Fh 90h 11-xxx-xxx DirectPath FADD 2

PFCMPGE mmreg, mem64 0Fh, 0Fh 90h mm-xxx-xxx DirectPath FADD 4

PFCMPGT mmreg1, mmreg2 0Fh, 0Fh A0h 11-xxx-xxx DirectPath FADD 2

PFCMPGT mmreg, mem64 0Fh, 0Fh A0h mm-xxx-xxx DirectPath FADD 4

PFMAX mmreg1, mmreg2 0Fh, 0Fh A4h 11-xxx-xxx DirectPath FADD 2

PFMAX mmreg, mem64 0Fh, 0Fh A4h mm-xxx-xxx DirectPath FADD 4

PFMIN mmreg1, mmreg2 0Fh, 0Fh 94h 11-xxx-xxx DirectPath FADD 2

PFMIN mmreg, mem64 0Fh, 0Fh 94h mm-xxx-xxx DirectPath FADD 4

PFMUL mmreg1, mmreg2 0Fh, 0Fh B4h 11-xxx-xxx DirectPath FMUL 4

PFMUL mmreg, mem64 0Fh, 0Fh B4h mm-xxx-xxx DirectPath FMUL 6

PFRCP mmreg1, mmreg2 0Fh, 0Fh 96h 11-xxx-xxx DirectPath FMUL 3

PFRCP mmreg, mem64 0Fh, 0Fh 96h mm-xxx-xxx DirectPath FMUL 5

PFRCPIT1 mmreg1, mmreg2 0Fh, 0Fh A6h 11-xxx-xxx DirectPath FMUL 4

PFRCPIT1 mmreg, mem64 0Fh, 0Fh A6h mm-xxx-xxx DirectPath FMUL 6

PFRCPIT2 mmreg1, mmreg2 0Fh, 0Fh B6h 11-xxx-xxx DirectPath FMUL 4

PFRCPIT2 mmreg, mem64 0Fh, 0Fh B6h mm-xxx-xxx DirectPath FMUL 6

PFRSQIT1 mmreg1, mmreg2 0Fh, 0Fh A7h 11-xxx-xxx DirectPath FMUL 4

Notes:

1. For the PREFETCH and PREFETCHW instructions, the mem8 value refers to an address in the 64-byte line to

be prefetched.

2. The byte listed in the column titled ‘imm8’ is actually the opcode byte.