Appendix C Instruction Latencies 271

Software Optimization Guide for AMD64 Processors

25112 Rev. 3.06 September 2005

Interpreting Placeholders

The Syntax column for an instruction entry shows the mnemonic for the instruction followed by any

operands. Items in italics are placeholders for operands that you must provide. A placeholder

indicates the size and type of operand that is allowed.

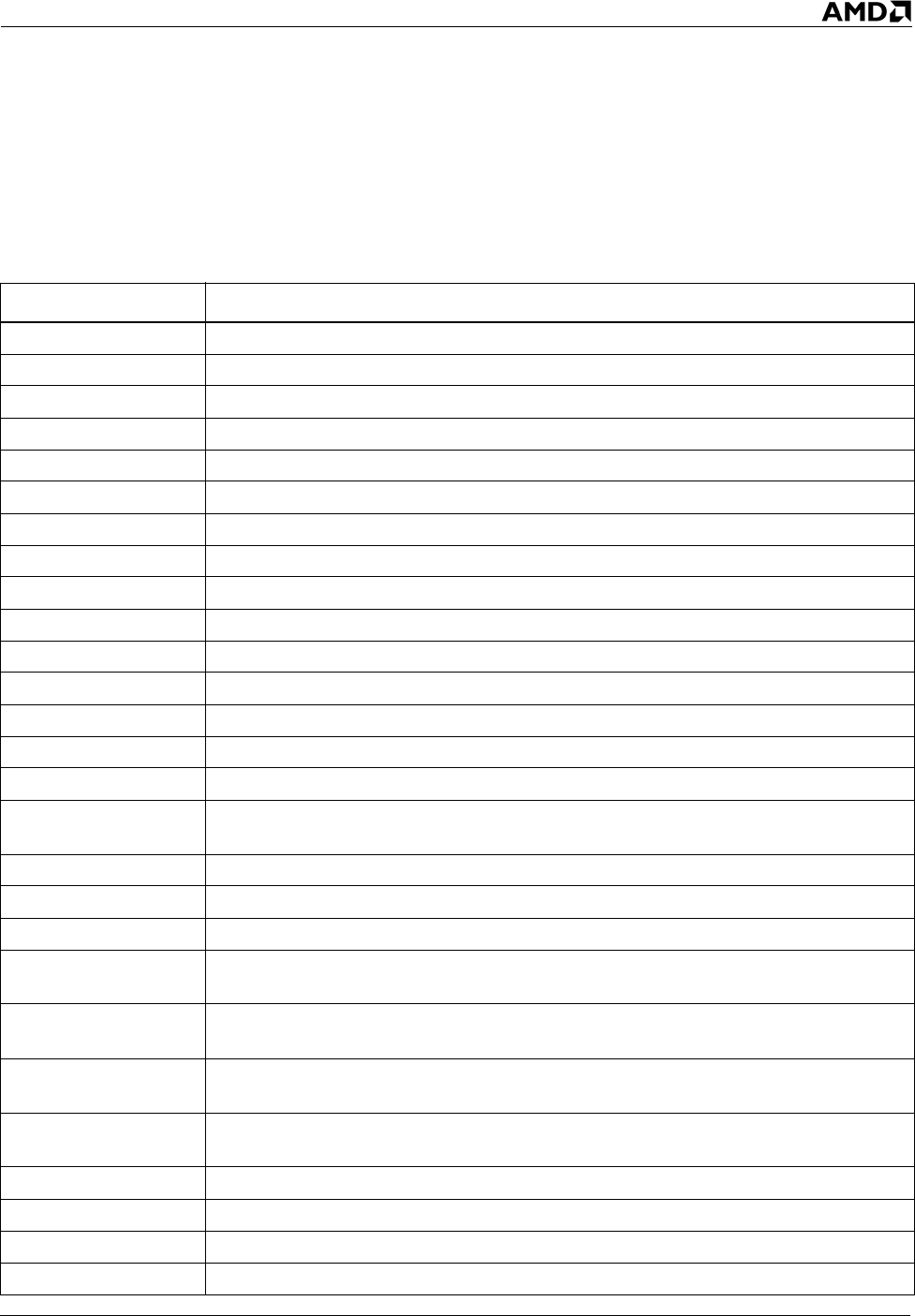

This operand Is a placeholder for

disp8 A byte (8-bit) displacement value

disp16/32 A word (16-bit) or doubleword (32-bit) displacement value

disp32/48 A doubleword (32-bit) or 48-bit displacement value

imm8 A byte (8-bit) immediate value

imm16 A word (16-bit) immediate value

imm32 A doubleword (32-bit) immediate value

mem8 A byte (8-bit) memory location

mem16/32/64 A memory location that contains a word, doubleword, or quadword

mem16/32&mem16/32 A memory location that contains a pair of words or doublewords

mem32/48 A doubleword (32-bit) or 48-bit memory location

mem48 A 48-bit memory location

mem64 A quadword (64-bit) memory location

mem128 A double quadword (128-bit) memory location

mem32real A memory location that contains a single-precision (32-bit) floating-point value

mem64real A memory location that contains a double-precision (64-bit) floating-point value

mem80real A memory location that contains a double-extended-precision (80-bit) floating-point

value

mmreg An MMX™ register

mmreg1 An MMX register defined by bits 5, 4, and 3 of the ModRM byte

mmreg2 An MMX register defined by bits 2, 1, and 0 of the ModRM byte

mreg8 A byte general-purpose register defined by the r/m field (bits 2, 1, and 0) of the

ModRM byte

mreg16/32/64 A word, doubleword, or quadword general-purpose register defined by the r/m field

(bits 2, 1, and 0) of the ModRM byte

reg8 A byte general-purpose register defined by instruction byte(s) or the reg field (bits 5,

4, and 3) of the ModRM byte

reg16/32/64 A word, doubleword, or quadword general-purpose register defined by instruction

byte(s) or the reg field (bits 5, 4, and 3) of the ModRM byte

sreg A segment register (always 16 bits wide)

xmmreg An XMM register

xmmreg1 An XMM register defined by bits 5, 4, and 3 of the ModRM byte

xmmreg2 An XMM register defined by bits 2, 1, and 0 of the ModRM byte