Appendix C Instruction Latencies 269

Software Optimization Guide for AMD64 Processors

25112 Rev. 3.06 September 2005

Appendix C Instruction Latencies

This appendix provides a complete listing of all AMD64 instructions, along with their encodings,

decode types, and execution latencies. For more information on these instructions, see volumes 3, 4,

and 5 of the AMD64 Architecture Programmer’s Manual (order# 24594, 26568, and 26569).

Note: Some prior AMD documents referred to one group of instructions as MMX™ technology

extensions. Those instructions are still supported by the AMD Athlon™ 64 and

AMD Opteron™ processors, but are documented with the SSE instructions in this guide. (The

MMX™ technology instructions remain a separate group.)

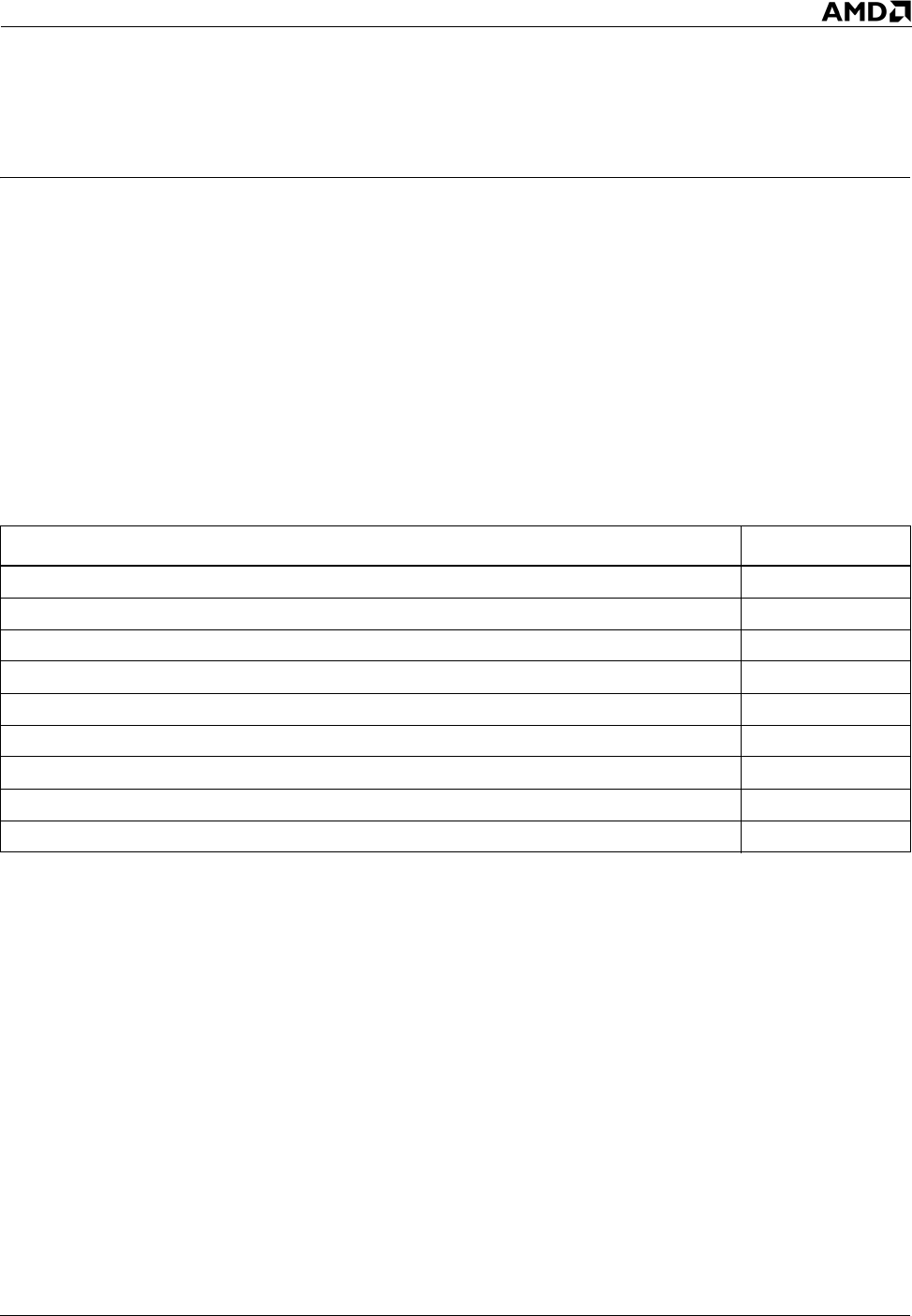

The instruction entries in this appendix are grouped into categories as indicated in the following table

and are presented within each category in alphabetical order by mnemonic:

Topic Page

Understanding Instruction Entries 270

Integer Instructions 273

MMX™ Technology Instructions 303

x87 Floating-Point Instructions 307

3DNow!™ Technology Instructions 314

3DNow!™ Technology Extensions 316

SSE Instructions 317

SSE2 Instructions 326

SSE3 Instructions 342