Appendix C Instruction Latencies 275

Software Optimization Guide for AMD64 Processors

25112 Rev. 3.06 September 2005

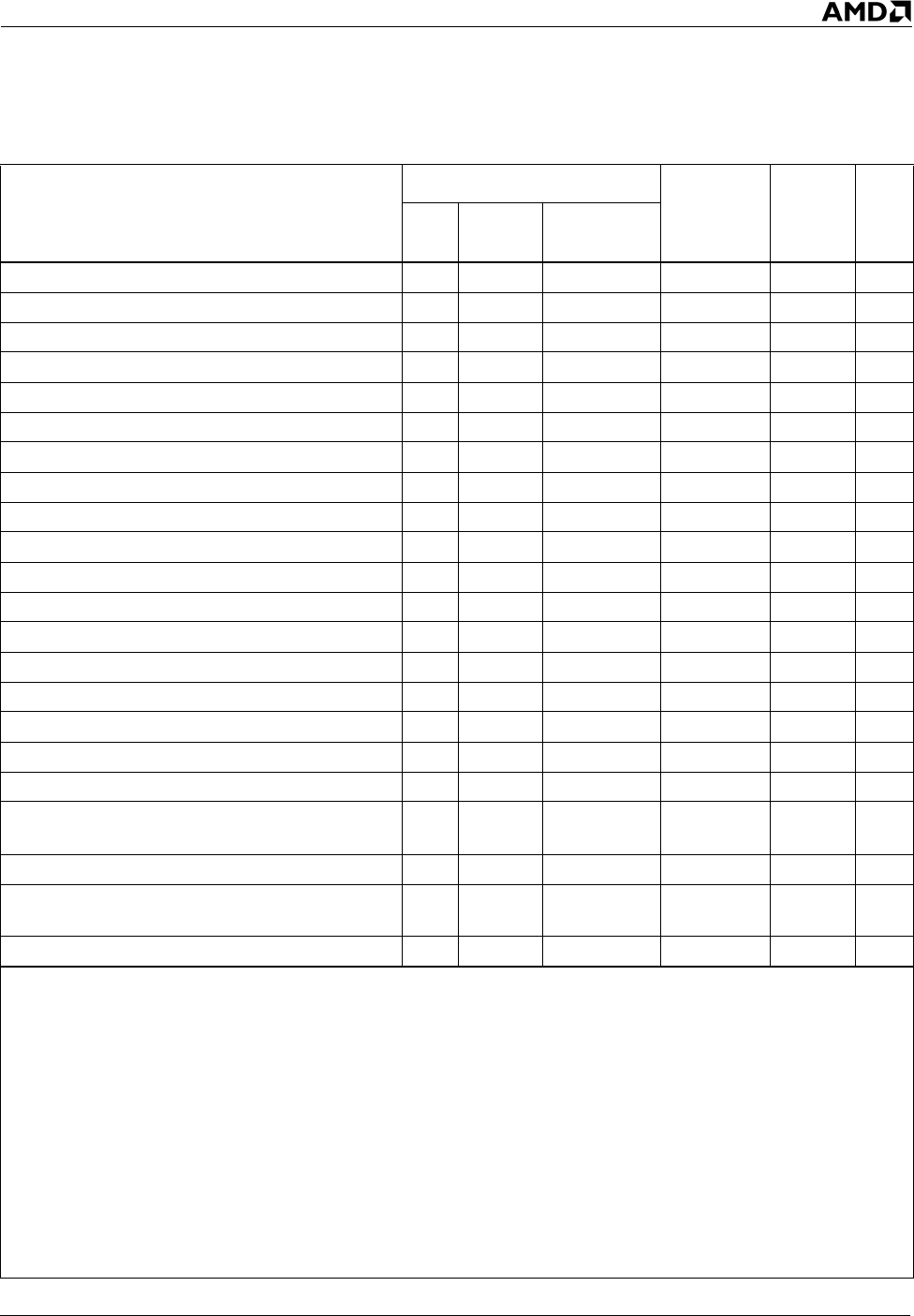

AND reg8, mreg8 22h 11-xxx-xxx DirectPath 1

AND reg8, mem8 22h mm-xxx-xxx DirectPath 4

AND reg16/32/64, mreg16/32/64 23h 11-xxx-xxx DirectPath 1

AND reg16/32/64, mem16/32/64 23h mm-xxx-xxx DirectPath 4

AND AL, imm8 24h DirectPath 1

AND AX, imm16 25h DirectPath 1

AND EAX, imm32 25h DirectPath 1

AND RAX, imm32 (sign extended) 25h DirectPath 1

AND mreg8, imm8 80h 11-100-xxx DirectPath 1

AND mem8, imm8 80h mm-100-xxx DirectPath 4

AND mreg16/32/64, imm16/32 81h 11-100-xxx DirectPath 1

AND mem16/32/64, imm16/32 81h mm-100-xxx DirectPath 4

AND mreg16/32/64, imm8 (sign extended) 83h 11-100-xxx DirectPath 1

AND mem16/32/64, imm8 (sign extended) 83h mm-100-xxx DirectPath 4

ARPL mreg16, reg16 63h 11-xxx-xxx VectorPath 13

ARPL mem16, reg16 63h mm-xxx-xxx VectorPath 18

BOUND reg16/32, mem16/32&mem16/32 62h mm-xxx-xxx VectorPath 6

BSF reg16/32/64, mreg16/32/64 0Fh BCh 11-xxx-xxx VectorPath 8/8/9

BSF reg16/32/64, mem16/32/64 0Fh BCh mm-xxx-xxx VectorPath 10/11/

12

BSR reg16/32/64, mreg16/32/64 0Fh BDh 11-xxx-xxx VectorPath 11

BSR reg16/32/64, mem16/32/64 0Fh BDh mm-xxx-xxx VectorPath 14/13/

13

BSWAP EAX/RAX/R8 0Fh C8h DirectPath 1

Table 13. Integer Instructions (Continued)

Syntax

Encoding

Decode

type

Latency Note

First

byte

Second

byte

ModRM

byte

Notes:

1. Static timing assumes a predicted branch.

2. Store operation also updates ESP—the new register value is available one clock earlier than the specified

latency.

3. The clock count, regardless of the number of shifts or rotates, as determined by CL or imm8.

4. LEA instructions have a latency of 1 when there are two source operands (as in the case of the base + index

form LEA EAX, [EDX+EDI]). Forms with a scale or more than two source operands will have a latency of 2 (LEA

EAX, [EBX+EBX*8]).

5. These instructions have an effective latency as shown. They map to internal NOPs that can be issued at a rate of

three per cycle but do not occupy execution resources.

6. The latency of repeated string instructions can be found in “Latency of Repeated String Instructions” on

page 167.

7. The first latency value is for 32-bit mode. The second is for 64-bit mode.

8. This opcode is used as a REX prefix in 64-bit mode.