272 Instruction Latencies Appendix C

25112 Rev. 3.06 September 2005

Software Optimization Guide for AMD64 Processors

Interpreting Latencies

The Latency column for an instruction entry shows the static execution latency for the instruction.

The static execution latency is the number of clock cycles it takes to execute the serially dependent

sequence of micro-ops that comprise the instruction.

The latencies in this appendix are estimates and are subject to change. They assume that:

• The instruction is an L1-cache hit that has already been fetched and decoded, with the operations

loaded into the scheduler.

• Memory operands are assumed to be in the L1 data cache.

• There is no contention for execution resources or load-store unit resources.

The following formats are used to indicate the static execution latency:

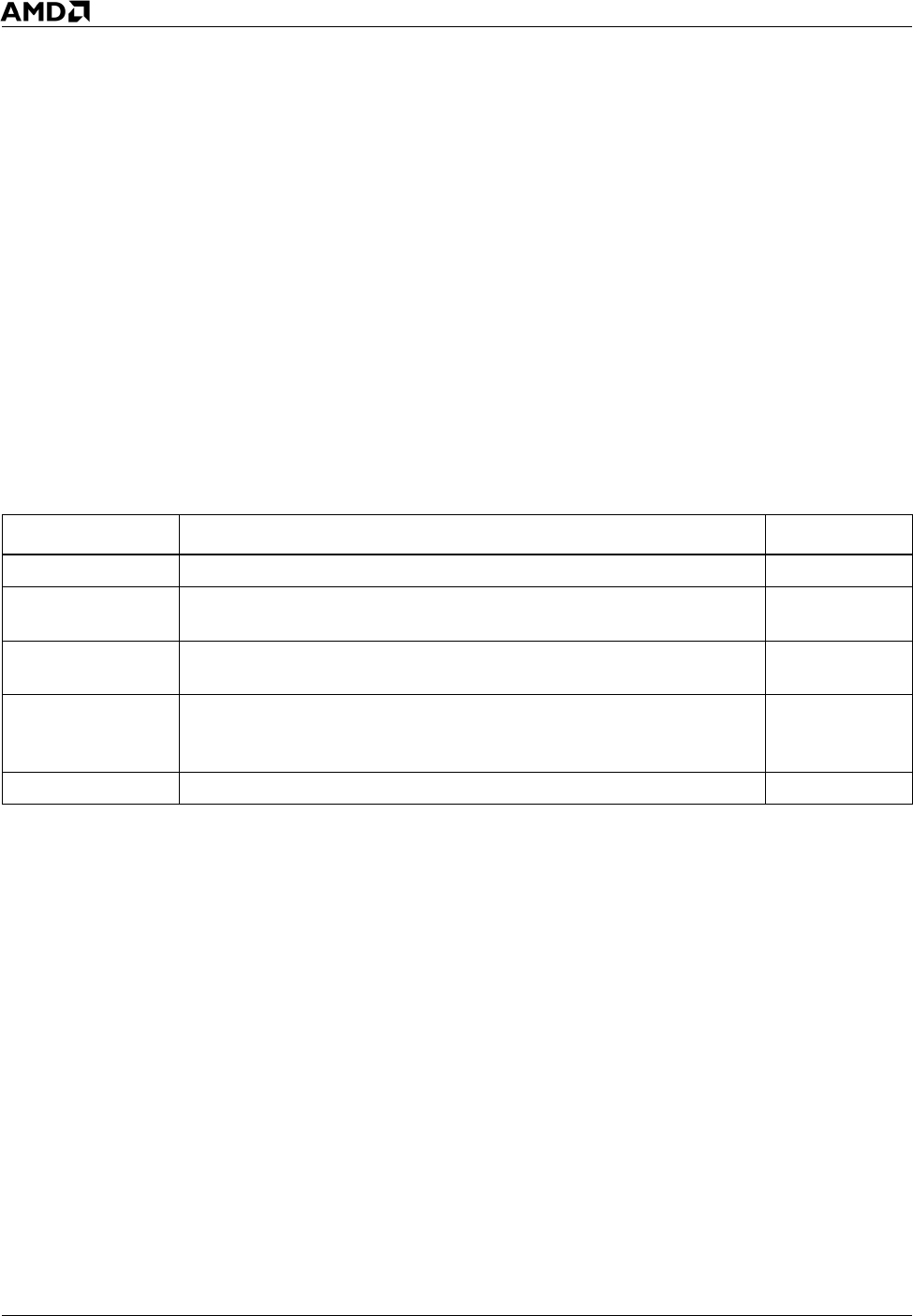

Latency format Description Example

x The latency is the indicated value. 3

x–y The latency is a value greater than or equal to x and less than or

equal to y.

31–73

x/y/z The latency differs according to the size of the operands. The values

x, y, and z are the 16-, 32-, and 64-bit latencies, respectively.

26/42/74

x (y) The latency depends on whether an error condition exists. When

there is no error condition, x is the latency. When an error condition

exists, y is the latency.

68 (108)

~ The latency is unavailable.