www.ti.com

PRODUCT PREVIEW

PCLK

2

1

3

4

4

TMS320DM355

DigitalMediaSystem-on-Chip(DMSoC)

SPRS463A–SEPTEMBER2007–REVISEDSEPTEMBER2007

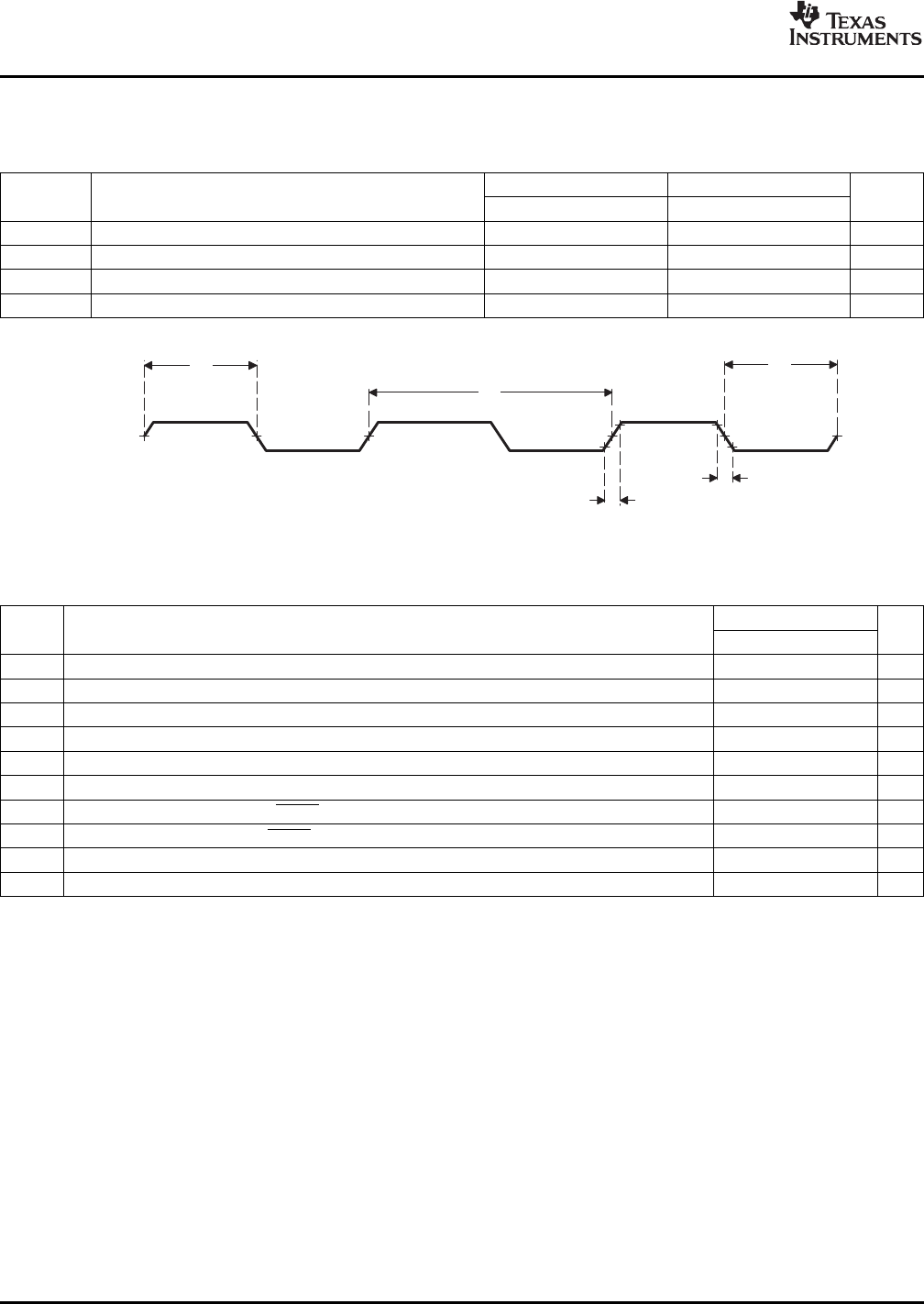

5.9.1.4VPFEElectricalData/Timing

Table5-17.TimingRequirementsforVPFEPCLKMaster/SlaveMode(seeFigure5-23)

DM355-216DM355-270

NO.UNIT

MINMAXMINMAX

1t

c(PCLK)

Cycletime,PCLK

(1)

18.5210014.81100ns

2t

w(PCLKH)

Pulseduration,PCLKhigh5.75.7ns

3t

w(PCLKL)

Pulseduration,PCLKlow5.75.7ns

4t

t(PCLK)

Transitiontime,PCLK33ns

(1)ThePCLKfrequencymustbelessthanorequaltohalftheVPSSclockfrequency—i.e.,PCLK≤SYSCLK4/2.

Figure5-23.VPFEPCLKTiming

Table5-18.TimingRequirementsforVPFE(CCD)SlaveMode(seeFigure5-24)

DM355

NO.UNIT

MINMAX

5t

su(CCDV-PCLK)

Setuptime,CCDvalidbeforePCLKedge3ns

6t

h(PCLK-CCDV)

Holdtime,CCDvalidafterPCLKedge2ns

7t

su(HDV-PCLK)

Setuptime,HDvalidbeforePCLKedge3ns

8t

h(PCLK-HDV)

Holdtime,HDvalidafterPCLKedge2ns

9t

su(VDV-PCLK)

Setuptime,VDvalidbeforePCLKedge3ns

10t

h(PCLK-VDV)

Holdtime,VDvalidafterPCLKedge2ns

11t

su(C_WEV-PCLK)

Setuptime,C_WEvalidbeforePCLKedge3ns

12t

h(PCLK-C_WEV)

Holdtime,C_WEvalidafterPCLKedge2ns

13t

su(C_FIELDV-PCLK)

Setuptime,C_FIELDvalidbeforePCLKedge3ns

14t

h(PCLK-C_FIELDV)

Holdtime,C_FIELDvalidafterPCLKedge2ns

PeripheralInformationandElectricalSpecifications 118SubmitDocumentationFeedback