www.ti.com

PRODUCT PREVIEW

3.6.3PLLC2

PLLDIV1(/1)

1

0

PLL

0

1

CLKMODE

CLKIN

OSCIN

PLLEN

SYSCLK1

(DDRPHY)

SYSCLKBP

(CLKOUT3)

BPDIV(/8)

PLLM

(programmable)

Pre-DIV

(programmable)

Post-DIV

(/1)

TMS320DM355

DigitalMediaSystem-on-Chip(DMSoC)

SPRS463A–SEPTEMBER2007–REVISEDSEPTEMBER2007

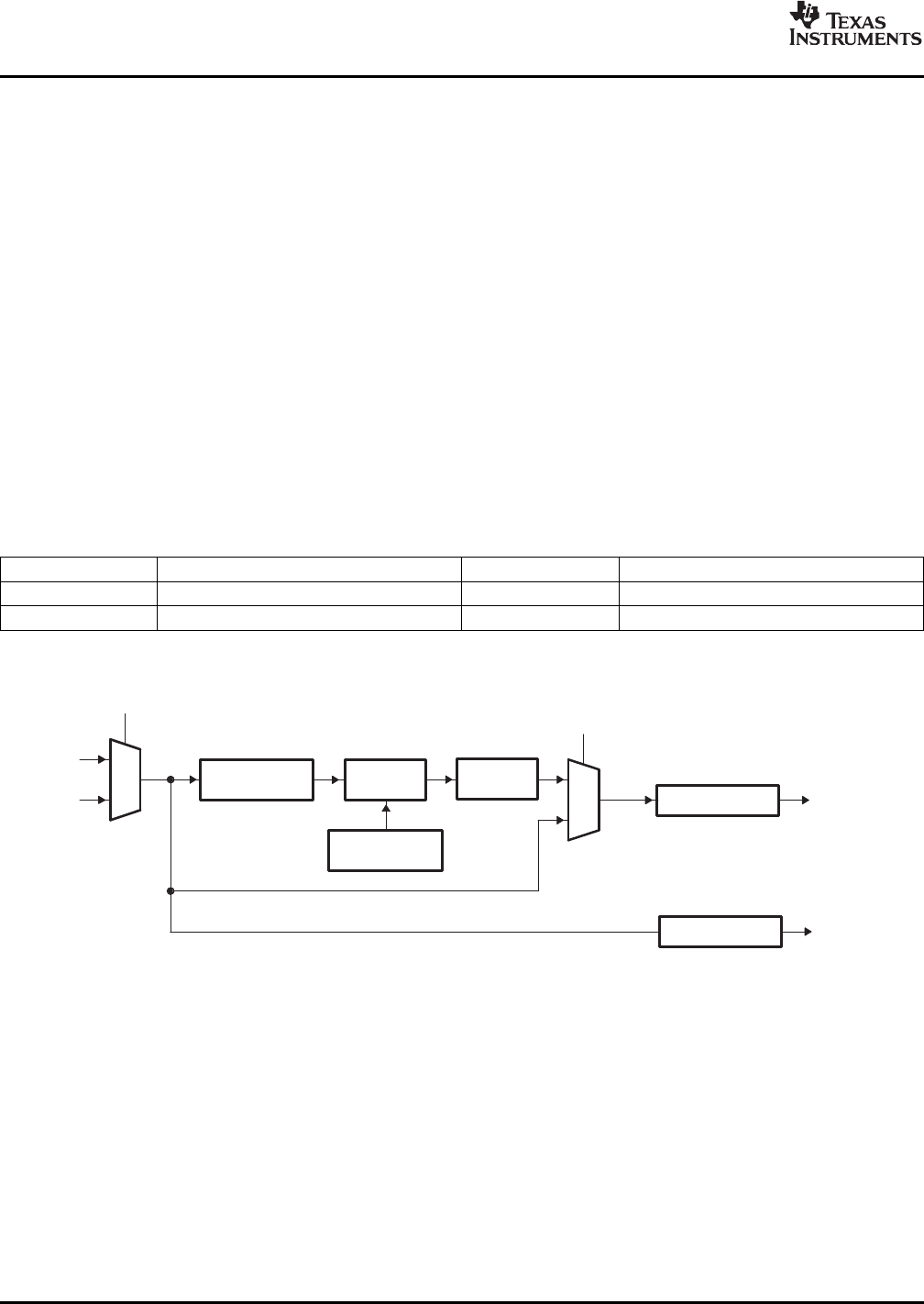

PLLC2providestheDDRPHYclockandCLKOUT3.SoftwarecontrolsPLLC2operationthroughthe

PLLC2registers.Thefollowinglist,Table3-11,andFigure3-4describethecustomizationsofPLLC2in

theDM355.

•ProvidesDDRPHYclockandCLKOUT3

•Softwareconfigurable

•Acceptsclockinputorinternaloscillatorinput(sameinputasPLLC1)

•PLLpre-dividervalueisprogrammable

•PLLmultipliervalueisprogrammable

•PLLpost-dividervalueisfixedto(/1)

•OnlySYSCLK[1]isused

•SYSCLK1dividervalueisfixedto(/1)

•SYSCLKBPdividervalueisfixedto(/8)

•SYSCLK1isroutedtotheDDRPHY

•SYSCLKBPisroutedtotheoutputpinCLKOUT3

•AUXCLKisnotused.

Table3-11.PLLC2OutputClocks

OutputClockUsedbyPLLDIVDividerNotes

SYSCLK1DDRPHY/1Fixeddivider

SYSCLKBPCLKOUT3/8Fixeddivider

PLLC2ConfigurationinDM355

DetailedDeviceDescription 76SubmitDocumentationFeedback