www.ti.com

PRODUCT PREVIEW

5.12SerialPortInterface(SPI)

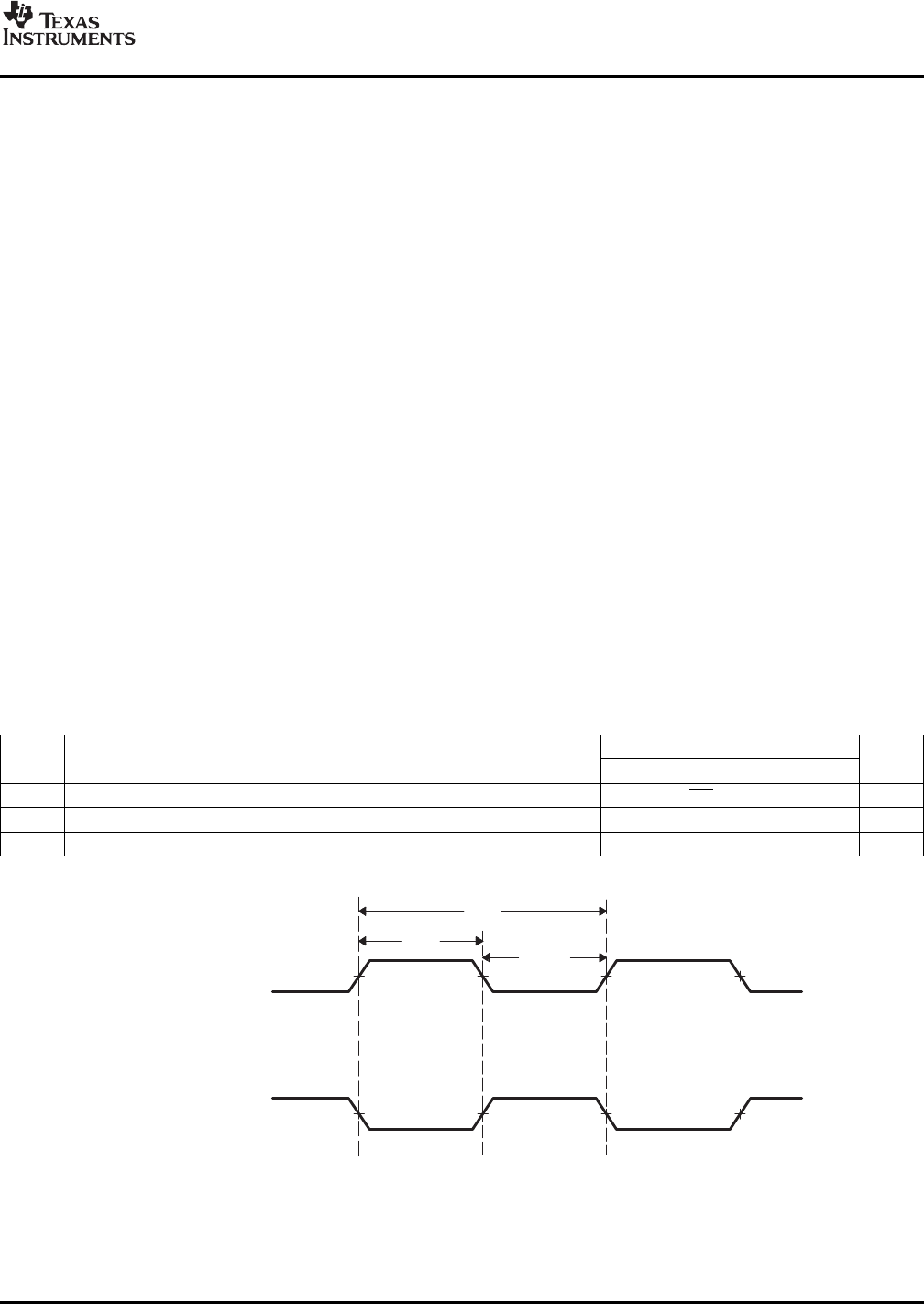

5.12.1SPIElectricalData/Timing

SPIx_CLK

(ClockPolarity=0)

1

2

3

SPIx_CLK

(ClockPolarity=1)

TMS320DM355

DigitalMediaSystem-on-Chip(DMSoC)

SPRS463A–SEPTEMBER2007–REVISEDSEPTEMBER2007

Thecontains3separateSPImodules.Thesemodulesprovideaprogrammablelengthshiftregisterwhich

allowsserialcommunicationwithotherSPIdevicesthrougha3or4wireinterface(Clock,DataIn,Data

Out,andEnable).TheSPIsupportsthefollowingfeatures:

•Mastermodeoperation

•2chipselectsforinterfacingtomultipleslaveSPIdevices.

•3or4wireinterface(Clock,DataIn,DataOut,andEnable)

•UniqueinterruptforeachSPIport

•SeparateDMAeventsforSPIReceiveandTransmit

•16-bitshiftregister

•Receivebufferregister

•Programmablecharacterlength(2to16bits)

•ProgrammableSPIclockfrequencyrange

•8-bitclockprescaler

•Programmableclockphase(delayornodelay)

•Programmableclockpolarity

TheSPImodulesdonotsupportthefollowingfeatures:

•Slavemode.OnlyMastermodeissupportedinDM355(MastermodemeansthatDM355providesthe

serialclock).

•GPIOmode.GPIOfunctionalityissupportedbytheGIOmodulesforthoseSPIpinsthatare

multiplexedwithGPIOsignals.

Table5-28.TimingRequirementsforSPI(AllModes)

(1)

(seeFigure5-36)

DM355

NO.UNIT

MINMAX

1t

c(CLK)

Cycletime,SPI_CLK37.037nsns

2t

w(CLKH)

Pulseduration,SPI_CLKhigh(AllMasterModes)0.45*T0.55*Tns

3t

w(CLKL)

Pulseduration,SPI_CLKlow(AllMasterModes0.45*T0.55*Tns

(1)T=t

c(CLK)

=SPI_CLKperiodisequaltotheSPImoduleclockdividedbyaconfigurabledivider.

Figure5-36.SPI_CLKTiming

SubmitDocumentationFeedbackPeripheralInformationandElectricalSpecifications131